أوضح CPLD: دليل للأجهزة المنطقية القابلة للبرمجة

في العالم الديناميكي للتصميم الإلكتروني ، تبرز أجهزة المنطق المعقدة القابلة للبرمجة (CPLDS) كأدوات متعددة الاستخدامات ، ومزج القدرة على التكيف ، والدقة ، والكفاءة.أحدثت هذه الأجهزة ثورة في تصميم الدوائر من خلال إدخال خلايا ماكرو قابلة للبرمجة ومصفوفة متداخلة مهيمنة ، مما يتيح إنشاء وظائف منطقية معقدة مع موثوقية ملحوظة.منذ إنشائهم في الثمانينيات إلى دورهم الرئيسي في الصناعات الحديثة مثل الشبكات والسيارات والفضاء ، أثبتت CPLDs أن تسعى للحصول على كل من المرونة والأداء.هذه المقالة تنطلق في رحلة CPLDs ، وميزاتها المميزة ، والتطبيقات العملية ، ومنهجيات البرمجة التي تجعلها حجر الزاوية في تصميم المنطق الرقمي.كتالوج

نظرة عامة على CPLD

ضمن السيطرة على الأجهزة المنطقية القابلة للبرمجة المعقدة (CPLDS) ، يكتشف المرء نسيجًا متطورًا من الخلايا الكلية المنطقية القابلة للبرمجة ، متداخلة من خلال مصفوفة متداخلة مهيمنة.تتيح لك خطوط وحدة الخلايا الماكرو (MC) وخطوط الإدخال/الإخراج (I/O) تصميم دوائر ببراعة ، وتكوين الهياكل للوظائف الفريدة.على عكس الأجهزة التي تحيرها توقيت الترابط المعقد ، تستخدم CPLDs الأسلاك المعدنية غير المنقولة.هذه المميزة تمنحهم سلوكًا ثابتًا ومتوقعًا على مدار الساعة ، مما يجعل التنبؤات التوقيت أكثر موثوقية ودقة.

الرحلة والاستخدام

البشر في السبعينيات ظهور أجهزة المنطق القابلة للبرمجة (PLDs) ، مما يعزز تحرك نحو وحدات ماكرو قابلة للبرمجة.أدخل هذا التحول مرونة في التصميم الواسعة ، ووضعها بصرف النظر عن الدوائر الرقمية الثابتة ، على الرغم من أن فائدتها كانت مقيدة في البداية على دوائر أبسط.أحدث ظهور CPLDS في منتصف الثمانينيات ثورة في هذا المشهد ، مما يمهد الطريق لتصميمات الدوائر المعقدة.منذ ذلك الحين ، نسجوا أنفسهم في نسيج الصناعات مثل الشبكات وإلكترونيات السيارات وتصنيع CNC وأنظمة الفضاء.يمكنك أن تتذكر الطريقة التي أبسلت بها CPLDs العمليات التي طالبت ذات مرة بدقة العمل اليدوي الدقيق ، مما يمثل قفزة رائعة في الكفاءة.

صفات مميزة من CPLDS

تميز CPLDs نفسها من خلال برامجها القابلة للتكيف ، والتكامل المكثف ، وقدرات التنمية السريعة ، وقابلية التطبيق الواسعة ، إلى جانب تكاليف الإنتاج الاقتصادي.إنهم يروقون لأولئك الذين لديهم خبرة في الحد الأدنى للأجهزة ، ويكونون بمثابة منتجات موثوقة وآمنة لا تتطلب اختبارًا شاملاً.كدليل على براعتهم في تصميمات الدوائر على نطاق واسع ، تلعب CPLDs دورًا رئيسيًا في تطوير النموذج الأولي وتقدم يقل عن 10000 وحدة ، مما يجسد لك كفاءة مفيدة لك.غالباً ما تكسب المهارة التي تتكيف بها CPLDs مع مطالب المشروع المتطور تقديرهم ، مع التأكيد على تعدد استخداماتها الفعلي في البيئات الديناميكية.

طرق التطبيق

تتيح لك هذه الدوائر المتكاملة توضيح وظائف المنطق المصممة لتلبية احتياجاتهم باستخدام كل من المخططات والأجهزة الوصف لغات على منصات التطوير.على سبيل المثال ، في تصميم جهاز الرد ، يتم إعداد أو وصف الأجهزة وتجميعها على جهاز كمبيوتر.باستخدام كبل تنزيل ، يتم نقل الرمز إلى CPLD للبرمجة داخل النظام ، والتي تضم اختبار التصميمات واستكشاف الأخطاء وإصلاحها وتعزيزها.ثم يتم إنتاج التصميمات المصنوعة بنجاح كبير عن طريق تكرار رقائق CPLD.في مشاريع مثل أنظمة إشارات المرور ، يصبح تكرار عملية التصميم أمرًا ضروريًا ، على غرار إعادة بناء منزل لاستعادة حداثة.غالبًا ما تضع هذه المنهجية المتكررة الأساس لإتقان ، وتعزيز المهارات والثقة.

المتغيرات الرائدة

على مر السنين ، كشفت شركات مثل Altera و Lattice و Xilinx عن خطوط بارزة من CPLDs.تشمل الأمثلة الجديرة بالملاحظة Altera's EPM7128S، شعرية LC4128Vو Xilinx's XC95108 .وجدت هذه النماذج أدوارًا بارزة عبر تطبيقات عالمية متنوعة.أولئك الذين لديهم امتياز العمل مع هذه المنتجات المتميزة في كثير من الأحيان يلاحظون على الاختلافات الدقيقة ولكن القوية التي تعمل على تحسين وظائف معينة.هذا يعكس عملية اختيار دقيقة تتأثر بمتطلبات محددة للمشروع ، حيث يحمل كل متغير جاذبيته الفريدة.

تحديد وتصنيف FPGA و CPLD

|

وجه |

CPLD |

FPGA |

|

تشكيل السلوك المنطقي |

تشكيل السلوك المنطقي باستخدام بنية مصطلح المنتج.

أمثلة: سلسلة شعرية ISPLSI ، سلسلة XILINX XC9500 ، Altera MAX7000S

سلسلة ، سلسلة Lattice Mach |

تشكيل السلوك المنطقي باستخدام طريقة البحث الجدول.

أمثلة: سلسلة Xilinx Spartan ، سلسلة Altera Flex10K ، ACEX1K |

|

ملاءمة |

مناسبة للخوارزميات والمنطق التوافقي ، تعمل

أفضل مع مشغلات محدودة وشروط المنتجات الغنية |

مناسب للمنطق المتسلسل ، يعمل بشكل أفضل مع

هياكل غنية بالمشغلات |

|

تأخير التوقيت |

يوفر هيكل الأسلاك المستمر موحدًا و

تأخير توقيت يمكن التنبؤ به |

يؤدي هيكل الأسلاك المجزأة إلى توقيت لا يمكن التنبؤ به

تأخير |

|

مرونة البرمجة |

يتم تعديل الدوائر الداخلية الثابتة للبرمجة.

يتم استخدام البرمجة المنطقية على مستوى الكتلة |

يتم تعديل الأسلاك الداخلية للبرمجة.منطق

تتيح البرمجة على مستوى البوابة مرونة أكبر |

|

اندماج |

انخفاض التكامل مقارنة مع FPGA |

تكامل أعلى مع بنية الأسلاك الأكثر تعقيدًا و

تنفيذ المنطق |

|

سهولة الاستخدام |

أسهل في الاستخدام مع البرمجة عبر e2prom أو fastflash.

لا يلزم وجود رقاقة ذاكرة خارجية |

يتطلب ذاكرة خارجية لتخزين البرمجة

المعلومات ، مما يؤدي إلى استخدام أكثر تعقيدًا |

|

السرعة والقدرة على التنبؤ |

سرعة أسرع وأفضل القدرة على التنبؤ بالتوقيت بسبب

ربط مترابطة بين كتل المنطق |

سرعة أبطأ وتوقيت أقل يمكن التنبؤ به بسبب

البرمجة على مستوى البوابة والتوصيل البيني الموزع |

|

تكنولوجيا البرمجة |

يستخدم E2Prom أو برمجة ذاكرة الفلاش.بيانات البرمجة

يتم الاحتفاظ بها عندما يتم تشغيل النظام.يدعم البرمجة على أ

مبرمج أو في النظام |

بناء على برمجة SRAM.يتم فقد بيانات البرمجة عندما

يتم تشغيل النظام ويجب إعادة تحميله.يدعم الديناميكية

إعدادات |

|

السرية |

يقدم سرية أفضل |

يوفر انخفاض السرية |

|

استهلاك الطاقة |

بشكل عام استهلاك الطاقة ، خاصة مع

تكامل أعلى |

انخفاض استهلاك الطاقة مقارنة مع CPLD |

لغات البرمجة من CPLD

إن تحليل كيفية برمجة الأجهزة المنطقية المعقدة (CPLDs) معقد هو حجر الزاوية في صياغة حلول الأجهزة متعددة الاستخدامات.اعتمدت الطرق التاريخية لبرمجة CPLDs على مخططات سلم أو لغات الوصف للأجهزة (HDLS) ، مع كون Verilog HDL و VHDL خيارات سائدة.يمكن أن تشكل اللغة المختارة كل من استراتيجية التصميم والكفاءة التشغيلية للتطبيقات.

• Verilog HDL: تعتز Verilog HDL ببناء بناء الجملة البسيط وقدرات محاكاة قوية ، مما يعكس المنهجيات المستخدمة في تصميم المنطق الرقمي.يتيح لك تكامله مع أدوات التصميم الإلكترونية (EDA) إجراء توليف ومحاكاة بسلاسة.وقد لوحظ أن بناء الجملة الشبيهة بـ C في Verilog يقلل من حاجز الدخول لأولئك الذين لديهم خلفيات برمجة ، مما يسارع الرحلة من التصميم إلى النشر عبر مجموعة واسعة من القطاعات الصناعية.

• VHDL: يوفر VHDL خيارًا أكثر تفصيلاً ومعبرة لبرمجة HDL.غالبًا ما يكون اختيار المشاريع التي تتطلب توثيقًا دقيقًا وتكيفًا صارمًا للسمات ، والسمات المقدرة في صناعات الفضاء والدفاع.يمكنك ملاحظة أنه على الرغم من التعقيد المحتمل لـ VHDL في المشاريع الأصغر ، فإن هيكلها المنضبط يدعم إنشاء تصميمات موثوقة بشكل استثنائي ، وهي ضرورة في البيئات التي تكون فيها السلامة هي المهيمنة.

معلومات عنا

ALLELCO LIMITED

قراءة المزيد

تحقيق سريع

الرجاء إرسال استفسار ، وسوف نرد على الفور.

NMOS Transistors: التصميم والتشغيل والتطبيقات

على 29/12/2024

تحويل فورييه السريع (FFT): إحداث ثورة في معالجة الإشارات الرقمية

على 29/12/2024

الوظائف الشعبية

-

أجهزة الكمبيوتر المعقدة لتعليمات التعليمات: كيف غيرت الحوسبة؟

على 19/04/8000 147782

-

usb-c pinout والميزات

على 19/04/2000 112062

-

باستخدام بدائل المحاكاة الموحدة Xilinx: دليل شامل لتصميم ومحاكاة FPGA

على 19/04/1600 111352

-

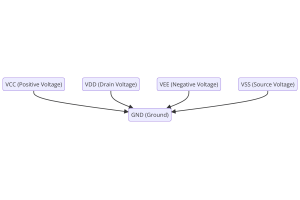

جهد مصدر الطاقة في الإلكترونيات: معنى VCC، VDD، VEE، VSS، وGND

على 19/04/0400 83819

-

دليل موصل RJ45: pinout ، الأسلاك ، أنواع الكابلات ، والاستخدامات

على 01/01/1970 79639

-

الدليل النهائي لرموز الألوان السلكية في الأنظمة الكهربائية الحديثة

الطريقة التي تستخدمها أنظمةنا الكهربائية بالألوان ليست فقط للمظهر.يشير كل لون سلك الآن إلى وظيفة محددة ، مما يسهل تحديد المكونات الكهربائية والتعامل معها بشكل صحيح أثناء التثبيت والصيانة.هذا لا يسر...على 01/01/1970 66999

-

دليل Purge Valve: الوظيفة والأعراض والاختبار والاستبدال لأداء المحرك الأمثل

يعد Purge Valve جزءًا رئيسيًا من نظام السيارة الذي يساعد في الحفاظ على نظافة الهواء من خلال إدارة أبخرة الوقود قبل أن يتمكنوا من الهروب إلى الجو.هذا لا يساعد البيئة فقط عن طريق تقليل التلوث ولكن أي...على 01/01/1970 63124

-

الجودة (س) العامل: المعادلات والتطبيقات

يعد عامل الجودة ، أو "Q" مهمًا عند التحقق من مدى عمل المحاثات والراتين في الأنظمة الإلكترونية التي تستخدم ترددات الراديو (RF).يقيس "Q" مدى تقليل الدائرة إلى تقليل فقدان الطاقة وتؤثر على نطاق التردد...على 01/01/1970 63062

-

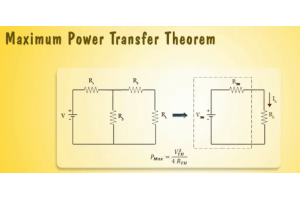

تحقيق ذروة أداء مع أقصى نظرية نقل الطاقة

تشرح نظرية نقل الطاقة القصوى كيف تتدفق الطاقة من مصدر ، مثل البطارية أو المولد ، إلى الحمل المتصل.يوضح الحالة الدقيقة التي يتلقى فيها الحمل أكثر الطاقة.تغطي هذه المقالة ما تعنيه النظرية ، وكيف تعمل...على 01/01/1970 54097

-

مواصفات البطارية A23 وتوافقها

بطارية A23 عبارة عن بطارية صغيرة على شكل أسطوانة مع جهد عالي.يُطلق عليه أيضًا 23a أو 23ae أو Mn21 ، ويتم تشغيله بسرعة 12 فولت وأعلى بكثير من بطاريات AA أو AAA.تصميمه الخاص يجعلها مثالية لل...على 01/01/1970 52215