EPF6016ATC144-2N FPGA: الميزات والبرمجة والتطبيقات والبدائل

هذا الدليل هو كل شيء عن EPF6016ATC144-2N ، وهو نوع من رقاقة تسمى FPGA.يتم استخدامه في الأنظمة الرقمية التي يجب أن تكون مرنة وسهلة التحديث.يشرح الدليل ما تفعله الشريحة ، وكيف تعمل ، وأجزائها الرئيسية وميزاتها ، وكيفية استخدامها وبرمجتها ، ومكان استخدامها ، ولماذا لا يزال خيارًا جيدًا اليوم.كتالوج

ما هو EPF6016ATC144-2N؟

ال EPF6016ATC144-2N هو عضو في عائلة Flex 6000 FPGA التي طورتها Altera ، وهي الآن جزء من Intel.تم تصميم هذا الجهاز على منطق إعادة برمجة قابلة لبرمجة SRAM للمرونة في تطبيقات المنطق الرقمي متوسطة الكثافة.إنه يعزز بنية Optiflex ، التي تجمع بين كتل المصفوفة المنطقية (LABS) ومصفوفة اتصال عالي السرعة لتقديم استخدام موارد فعال وتوجيه الإشارة السريعة.يدعم EPF6016ATC144-2N إعادة تكوين النظام ، مما يجعله مثاليًا للتصميمات التي تتطلب تحديثات أو تعديلات بعد النشر.كجزء من سلسلة Flex 6000 ، فإنه يوفر حلاً فعالًا من حيث التكلفة لاستبدال صفائف البوابة التقليدية مع تبسيط دورة التطوير.

هل تبحث عن EPF6016ATC144-2N؟اتصل بنا للتحقق من الأسهم الحالية ، وتهمة المهلة ، والتسعير.

EPF6016ATC144-2N CAD نماذج

EPF6016ATC144-2N الرمز

EPF6016ATC144-2N بصمة

EPF6016ATC144-2N 3D نموذج

EPF6016ATC144-2N الميزات

• القدرة المنطقية

يوفر EPF6016ATC144-2N حوالي 16000 بوابة نظام ، تم تنفيذها باستخدام 1،320 عنصرًا منطقيًا (LES) عبر 132 قطعة مصفوفة منطقية (LABS).يوفر هذا التعقيد المعتدل مناسبًا لتطبيقات FPGA متوسطة المدى.

• دبابيس I/O.

وهو يدعم ما يصل إلى 117 دبابيس إدخال/إخراج قابلة للتكوين.تتيح هذه المسامير الاتصال المرن بمكونات النظام المختلفة والأجهزة الخارجية.

• الجهد الأساسي

يعمل Core عند 3.3 فولت مع نطاق وظيفي من 3.0 فولت إلى 3.6 فولت. وهذا يسمح بالتوافق مع الأنظمة الرقمية القياسية منخفضة الجهد.

• I/O الجهد

تدعم ميزة I/O Multivolt الخاصة بها التواصل مع الأجهزة باستخدام مستويات 3.3V أو 2.5V.هذا يبسط التكامل في بيئات الجهد المختلط.

• درجة حرارة التشغيل

نطاق درجة حرارة تقاطع التشغيل القياسي هو 0 درجة مئوية إلى +85 درجة مئوية.هذا يدعم البيئات التجارية والصناعية النموذجية.

• توريد التيار

يرسم ما يقرب من 5 أمتار أثناء التشغيل العادي وأقل من 0.5mA في وضع الاستعداد.هذا يساعد على الحفاظ على الطاقة في التصميمات الواعية للطاقة.

• سرعة الساعة (درجة السرعة –2n)

مع درجة السرعة -2 ، يحقق ترددات منطقية داخلية تصل إلى حوالي 166 ميجا هرتز.هذا يتيح الحساب السريع في معالجة الإشارات أو منطق التحكم.

• بنيان

استنادًا إلى بنية Optiflex الخاصة بـ Altera ، فإنه يستخدم المنطق المستند إلى LUT مع موارد التوجيه المخصصة.توفر هذه البنية كثافة منطقية عالية وأداء فعال.

• Fasttrack interconnect

تتيح شبكة توجيه FastTrack مسارات الإشارة منخفضة التشكيل ودعم عمليات نقل البيانات عالية السرعة عبر كتل المنطق.هذا يساهم في التوقيت المتسق والأداء.

• إعادة تكوين الدائرة

يستخدم تكوين المنطق المستند إلى SRAM ، مما يسمح بإعادة برمجة FPGA في النظام.هذا يدعم تحديثات التصميم أو تكيف الأجهزة الديناميكية دون إزالة.

• مسح الحدود JTAG

يتضمن الجهاز منطق حدود JTAG المتوافق مع IEEE 1149.1.هذا يسهل تصحيح الأخطاء والاختبار في النظام للوحات والوصلات البينية.

• دعم الساخنة

يمكن إدخاله أو إزالته بأمان أثناء تشغيله في أنظمة 3.3 فولت.هذه الميزة مفيدة في منصات الأجهزة المعيارية أو القابلة للخدمة.

• اختبار وظيفي

يتم اختبار كل وحدة بشكل وظيفي بالكامل قبل الشحن.هذا يضمن الجودة ويزيل الحاجة إلى متجهات الاختبار المعرفة من قبل المستخدم أثناء التطوير.

• توافق PCI

يتوافق الجهاز مع PCI Local Bus Revision 2.2 لتشغيل 5V.يسمح ذلك باستخدامه في الأنظمة المضمنة القائمة على PCI.

مخطط كتلة العمارة Optiflex

يوضح الرسم البياني كيف يتم تنظيم الأجزاء الداخلية من FPGA وتوصيلها.في المركز توجد كتل صفيف منطقية (LABS) ، هذه هي وحدات البناء الرئيسية للرقاقة.يحتوي كل مختبر على العديد من العناصر المنطقية (LES) التي تؤدي العمليات الرقمية الأساسية ، مثل البوابات المنطقية و flip-flops.يتم توصيل المختبرات عن طريق ربط محلي ، مما يسمح للمنطق داخل كل كتلة بالعمل معًا بكفاءة.للاتصال الأوسع عبر الشريحة ، يرتبط المختبرات بالتوصيلات السريعة للصف والعمود ، ومسارات إشارة سريعة تتيح للبيانات أن تتحرك بسرعة من جزء من الشريحة إلى آخر مع تأخير منخفض.حول الحواف الخارجية من الرسم البياني هي عناصر الإدخال/الإخراج (IOES).تربط هذه المنطق الداخلي لـ FPGA بالأجهزة الخارجية عن طريق التحويل بين مستويات منطق الشريحة ومستويات الجهد المستخدمة بواسطة الأجهزة الأخرى.يعكس هذا التصميم ، مع كتله المعيارية ومسارات التوجيه عالية السرعة ، مرونة وأداء بنية Optiflex.

نموذج توقيت 6000 Flex

يوضح نموذج توقيت Flex 6000 كيف تتحرك الإشارات وتأخيرها أثناء سفرها عبر FPGA.يوجد في مركز النموذج عناصر منطقية (LES) ، والتي تقوم بمعالجة إشارات البيانات والتحكم مع توقيت محدد.يتصل كل LE بمسارات التوقيت مثل T_DATA_TO_REG و T_REG_TO_OUT ، والتي تحدد المدة التي يستغرقها الإشارات للدخول ، والمعالجة ، والخروج من المنطق.

بجانب LES توجد مسارات خاصة تسمى Lab Carry و Lab Cascade.تسمح هذه الإشارات بالتحرك أفقياً بين العناصر المنطقية في نفس الكتلة ، ودعم العمليات السريعة مثل الإضافات والمقارنات.تحتوي هذه المسارات أيضًا على قيم التوقيت الخاصة بها ، مثل T_CARRY_TO_REG و T_CASC_TO_OUT ، لقياس التأخير أثناء هذه العمليات.

في الجزء السفلي من المخطط ، تعامل عناصر الإدخال/الإخراج (IOES) إشارات تدخل وخارج الشريحة.وهي تشمل نقاط تأخير مثل T_IN_DELAY ، والتي تمثل الاختلافات عند تلقي البيانات من الأجهزة الخارجية.

يتضمن النموذج أيضًا مسارات التوجيه على مستويات مختلفة (T_LOCAL ، T_ROW ، T_COL ، و T_GLOBAL) يمثل كل منها إلى أي مدى تنتقل الإشارة ومقدار الوقت الذي تستغرقه.تساعد هذه المسارات في فهم وإدارة التأخير عبر أجزاء مختلفة من الشريحة ، مما يسهل تحقيق أهداف الأداء والتوقيت.

EPF6016ATC144-2N المواصفات

|

يكتب |

المعلمة |

|

الشركة المصنعة |

Altera/Intel |

|

مسلسل |

فليكس 6000 |

|

التغليف |

صينية |

|

حالة الجزء |

عفا عليها الزمن |

|

عدد المختبرات/CLBs |

132 |

|

عدد العناصر/الخلايا المنطقية |

1320 |

|

عدد i/o |

117 |

|

عدد البوابات |

16000 |

|

الجهد - العرض |

3V ~ 3.6V |

|

نوع التثبيت |

جبل السطح |

|

درجة حرارة التشغيل |

0 درجة مئوية ~ 85 درجة مئوية (TJ) |

|

حزمة / حالة |

144-LQFP |

|

حزمة جهاز المورد |

144-TQFP (20x20) |

|

رقم المنتج الأساسي |

EPF6016 |

تطبيقات EPF6016ATC144-2N

1. مهام معالجة الإشارات الرقمية (DSP)

من خلال 1،320 عنصر منطقي وربط سريع ، يدعم EPF6016ATC144-2N تنفيذ وظائف معالجة الإشارات الرقمية الصغيرة إلى المتوسطة المدى.يمكن استخدامه لإنشاء مرشحات FIR مخصصة ، أو نوى FFT ، أو المنطق الحسابي المتوازي لتحويل الإشارة.على الرغم من أنه يفتقر إلى كتل DSP المخصصة أو مضاعفات مضمونة ، إلا أن منطقها للأغراض العامة يمكن أن يتعامل مع عمليات التكرار المتكررة المتعددة المناسبة للمعالجة الصوتية المدمجة وتصفية بيانات المستشعر وتشكيل الموجة في أنظمة التحكم أو الاتصالات.

2. السيطرة المدمجة والأتمتة الصناعية

الجهاز مناسب تمامًا لتطبيقات التحكم المدمجة في البيئات الصناعية.إن قدرتها على التفاعل مع I/O (2.5 فولت و 3.3 فولت) ، وعملياتها المستقرة في ظل درجات الحرارة التجارية القياسية (0-85 درجة مئوية) ، ودعم الجوز الساخن تجعلها موثوقة للتكامل في وحدات التحكم المنطقية القابلة للبرمجة (PLCs) ، وحدات التحكم في المحرك ، وبيانات الأجهزة ، ومواد التشغيل الآلية العامة.تتيح إعادة التكوين مرونة في المنتج على المدى الطويل ، حيث يمكن تحديث المنطق دون استبدال الأجهزة.

3. سد بروتوكول الاتصالات ومنطق الواجهة

بفضل دعم إدخال/إخراج المتعدد وشبكة التوجيه الفعالة ، يمكن استخدام EPF6016ATC144-2N لتنفيذ واجهات الاتصال المخصصة ومحولات البروتوكول.يمكنه بناء UARTS أو وحدات التحكم SPI أو مترجمي الحافلات المتوازية لتمكين التفاعل بين الأنظمة الرقمية غير المتطابقة.تدعم عدد الإدخال/الإخراج المعتدل (117 GPIOS) وإدارة الساعة الداخلية الإشارات الحساسة للوقت ، مما يجعلها مناسبة لمعدات الشبكات ، ومضاهاة الحافلة القديمة ، أو كعنصر منطق غراء في أنظمة اتصال البيانات الأكبر.

4. اختبار مستوى مجلس الإدارة ، تصحيح الأخطاء ، والتحقق من الصحة

مع قدرة حدود JTAG المدمجة (IEEE 1149.1 متوافق) ، يدعم EPF6016ATC144-2N الاختبار المتقدم على مستوى المجلس دون طلب تحقيقات منطقية خارجية أو تشخيصات تدخلية.يمكن أن تتحقق من اتصال الإدخال/الإخراج ، واكتشاف الدوائر المفتوحة أو القصيرة ، وإجراء عمليات الفحص داخل النظام أثناء الإنتاج أو الصيانة الميدانية.هذه الميزة مفيدة في مركبات ثنائي الفينيل متعدد الكلور المعقدة متعددة الطبقات أو في الأنظمة التي يكون فيها الوصول التقليدي إلى نقاط الاختبار محدودة أو غير عملية.

EPF6016ATC144-2N أجزاء مماثلة

|

سمات |

EPF6016ATC100-1 |

EPF6016ATC100-3N |

EPF6016ATC144-3N |

|

الشركة المصنعة |

Altera |

Intel (altera legacy) |

Intel (altera legacy) |

|

عائلة |

فليكس 6000 |

فليكس 6000 |

فليكس 6000 |

|

العناصر المنطقية (LES) |

1،320 |

1،320 |

1،320 |

|

عدد البوابة (تقريبا) |

16000 |

16000 |

16000 |

|

طَرد |

100 دبوس TQFP |

100 دبوس TQFP |

144-Pin TQFP |

|

دبابيس I/O المستخدم |

81 |

81 |

117 |

|

درجة السرعة |

-1 (قياسي) |

-3n (سرعة عالية) |

-3n (سرعة عالية) |

|

الحد الأقصى لتكرار الساعة |

أقل (عادة ~ 100 ميجا هرتز) |

أعلى (تصل إلى 166 ميغاهيرتز) |

أعلى (تصل إلى 166 ميغاهيرتز) |

|

نوع التكوين |

SRAM على أساس |

SRAM على أساس |

SRAM على أساس |

|

جهد إمدادات الطاقة |

3.3 ضد |

3.3 ضد |

3.3 ضد |

|

الساخنة |

نعم |

نعم |

نعم |

|

JTAG/مسح الحدود |

نعم |

نعم |

نعم |

|

التطبيقات |

المنطق الأساسي ، التصاميم المدمجة |

منطق التحكم بشكل أسرع ، مضغوط |

أنظمة عالية الأداء ، المزيد من الإدخال/س |

|

توافر |

عفا عليها الزمن |

عفا عليها الزمن |

عفا عليها الزمن |

EPF6016ATC144-2N خطوات البرمجة

1. اختر وضع التكوين

يدعم EPF6016ATC144-2N التكوين المستند إلى SRAM ، مما يعني أنه يتطلب البرمجة على كل الطاقة.يسمح الجهاز بالعديد من مخططات التكوين ، الأكثر شيوعًا السلبي (PS) وغير المتزامن المتوازي السلبي (PPA).يتم تحديد وضع التكوين عن طريق توصيل دبوس MSEL.على سبيل المثال ، عندما يكون MSEL منخفضًا ، يتوقع الجهاز إرسال البيانات بشكل متسلسل عبر EEPROM الخارجي (مثل EPC1) أو كبل تنزيل.يعتمد اختيار طريقة التكوين الصحيحة على تصميم النظام ، أو المستند إلى EEPROM من أجل التمهيد التلقائي ، أو القائم على الكبل للنماذج الأولية والاختبار.

2. تجميع تصميم FPGA وإنشاء ملف برمجة

لبرمجة FPGA ، يجب عليك أولاً إنشاء تصميم الأجهزة الخاص بك باستخدام برنامج تصميم Intel أو Legacy Max+Plus II.بعد التجميع ، تقوم الأداة بإنشاء SOF (ملف كائن SRAM) الذي يمثل المنطق المكون.يجب بعد ذلك تحويل SOF إلى تنسيق متوافق مع طريقة التكوين التي اخترتها:

• .rbf أو .pof لأجهزة EEPROM (على سبيل المثال ، EPC1).

• .TTF أو.

يتم التحويل باستخدام أداة محول الملفات المدمجة في برنامج التصميم.تضمن هذه الخطوة أن يتم تنسيق BitStream بشكل صحيح لتفسير FPGA.

3. برمجة ذاكرة التكوين (إذا كنت تستخدم EEPROM)

في التطبيقات التي يتم فيها استخدام جهاز التكوين التسلسلي مثل EPC1 ، فإن الخطوة التالية هي تحميل بيانات التكوين في EEPROM.يتم ذلك عادةً باستخدام أداة برمجة سطح المكتب (على سبيل المثال ، مبرمج Max+Plus II أو مبرمج Quartus).تتضمن العملية وضع EEPROM في مقبس البرمجة أو توصيله داخل الدائرة ، وتحميل ملف البرمجة المناسب (عادةً .pof أو .rbf) ، وبدء دورة البرنامج.بمجرد البرمجة ، ستوفر EEPROM تلقائيًا بيانات التكوين إلى FPGA في كل مرة يقوم فيها النظام بتشغيل ، مما يلغي الحاجة إلى إعادة البرمجة اليدوية.

4. تكوين باستخدام كبل تنزيل (مسلسل سلبي)

يتمثل بديل في التمهيد المستند إلى EEPROM إلى استخدام كبل تنزيل (مثل USB-Blaster أو Byteblaster) لتكوين FPGA مباشرة.في هذه الطريقة ، تقوم بتوصيل الكبل بجهاز الكمبيوتر الخاص بك و FPGA's NCONFIG و DCLK و DATA و CONF_DONE.باستخدام مبرمج Quartus ، يمكنك بدء عملية التكوين ، والتي تنبض NCONFIG منخفضة للبدء.ثم ترسل الأداة بيانات التكوين بشكل تسلسلي من خلال خط البيانات ، الذي تم تسجيله بواسطة DCLK.تكتمل العملية عندما يرتفع Conf_done ، مما يشير إلى التكوين الناجح وانتقال الجهاز إلى وضع المستخدم.

5. تكوين باستخدام متحكم (مسلسل سلبي/متوازي)

إذا كان نظامك يستخدم متحكمًا مضمنًا ، فيمكنه أيضًا أن يكون بمثابة ماجستير تكوين FPGA.في هذا الإعداد ، يؤكد متحكم microcontroller NCONFIG منخفضًا لإعادة تعيين FPGA ، ثم يقوم بتحويل التكوين bitstream من خلال البيانات أثناء تبديل DCLK.يجب احترام متطلبات التوقيت ، ووقت إعداد البيانات قبل الساعة ووقت الاحتفاظ به بعد ذلك مفيدة للتكوين الناجح.يمكن لمكافحة متحكم مراقبة دبابيس Nstatus و conf_done للكشف عن أخطاء التكوين أو تأكيد الانتهاء الناجح.توفر هذه الطريقة تحكمًا كاملاً في عملية التكوين ويدعم التحديثات الديناميكية في الحقل.

6. مراقبة إشارات التكوين

أثناء عملية التكوين ، يوفر FPGA ملاحظات من خلال دبابيس الحالة:

• يشير nstatus إلى اكتشاف الأخطاء ؛ينخفض في حالة حدوث خطأ (على سبيل المثال ، خطأ CRC أو انتهاك التوقيت).

• Conf_done يرتفع بمجرد تحميل جميع بتات التكوين بنجاح والتحقق منها.

إذا ظل NSTATUS مرتفعًا و CONF_DONE يحولات عالية في نهاية التسلسل ، فإن الجهاز يدخل تلقائيًا في وضع المستخدم ، حيث يصبح المنطق المعرفة من قبل المستخدم نشطًا.تعد مراقبة الإشارة هذه مهمة لضمان اكتمال عملية البرمجة بنجاح.

7. أداء إعادة التكوين عند الحاجة

نظرًا لأن EPF6016ATC144-2N يعتمد على SRAM ، يمكن إعادة تكوينه في أي وقت عن طريق تبديل دبوس NCONFIG ، والذي يعيد تعيين الجهاز وإعادة تشغيل دورة التكوين.تتيح هذه الميزة تحديثات النظام المرنة والتغييرات أثناء التشغيل دون استبدال مادي.تدعم القدرة على إعادة التكوين أثناء دائرة الدائرة أيضًا التكرار أو تبديل الوظائف الديناميكية أو تصحيح الأخطاء بعد النشر.هذا يجعل الجهاز مناسبًا للغاية للتطبيقات التي تتطلب القدرة على التكيف أو طول العمر.

8. مراقبة التوقيت والمتطلبات الكهربائية

تتطلب برمجة EPF6016ATC144-2N بنجاح الاهتمام بالقيود الكهربائية والتوقيت.يجب أن تفي ساعة التكوين (DCLK) حدود التردد (على سبيل المثال ، عادة ما يصل إلى 10 ميغاهيرتز في أوضاع التسلسلية القياسية).يتطلب الجهاز تأخيرًا قصيرًا (حوالي 200 مللي ثانية) بعد زيادة الطاقة لإعادة ضبط الطاقة الداخلية لتحقيق الاستقرار.بالإضافة إلى ذلك ، يجب أن تكون جميع إشارات التكوين نظيفة وخالية من الضوضاء وإنهاءها بشكل صحيح.إذا كنت تستخدم مقبس الساخن ، فيجب توخي الحذر لضمان سلامة الإشارة والتسلسل السليم للطاقة و I/O.

EPF6016ATC144-2N مزايا

• فعالة من حيث التكلفة لتصميمات المعدات المتوسطة

يلفت EPF6016ATC144-2N توازنًا بين القدرة على تحمل التكاليف والوظائف ، مما يجعله مثاليًا للتصميمات التي تتطلب مرونة أكثر من المنطق الثابت ولكن لا تبرر النفقات أو القوة النفقات العامة لـ FPGAs المتطورة.

• تبسيط تصميم ثنائي الفينيل متعدد الكلور وتكامله

مقارنةً بـ FPGAs ذات الكثافة العالية التي تتطلب غالبًا حزم BGA ذات النبرة الدقيقة ، فإن EPF6016ATC144-2N يأتي في حزمة TQFP قياسية 144 دبوس.تعمل هذه العبوة على تبسيط كل من تصميم وتصنيع مركبات ثنائي الفينيل متعدد الكلور لأنها تتجنب الحاجة إلى أدوات التخطيط المتقدمة ، أو microvias ، أو لوحات العلف عالية الطبقات.كما أنه يسهل إعادة صياغة نقل اليدين أو إعادة صياغة أساسية ، وهو مفيد للفرق الأصغر أو المختبرات ذات القدرات المحدودة للتجميع.

• انخفاض خطر التقادم أثناء النشر

نظرًا لدعمها الطويل الأمد في التطبيقات الصناعية القديمة ، يظل EPF6016ATC144-2N متاحًا في العديد من الأسواق الثانوية ولا يزال مدعومًا على نطاق واسع في برامج التصميم مثل Quartus II و MAX+Plus II.بالنسبة للشركات التي تحتفظ بمنتجات LINFECYCLE الطويلة مثل أتمتة المصنع أو أنظمة القياس أو وحدات الاتصالات ، فإن هذا يضمن استمرار الوصول إلى السيليكون المعروف جيدًا دون الحاجة إلى إعادة تصميم الأجهزة حول FPGAs أحدث وأكثر تعقيدًا.

• سلوك موثوق

على عكس بعض FPGAs العالية الأداء العالية التي تعمل على هوامش ضيقة وهي حساسة للتقلبات في الطاقة ودرجة الحرارة ، فإن EPF6016ATC144-2N قوي ومتسامح مع الاختلافات البيئية الشائعة.إنه يعمل بشكل مريح عبر نطاق درجة الحرارة التجارية ويدعم مقبس الساخن ، مما يجعلها موثوقة في أنظمة معيارية أو قابلة للخدمة.هذه الموثوقية تجعلها خيارًا عمليًا للأنظمة التي تتطلب أداءً ثابتًا بمرور الوقت وتحت ظروف متغيرة.

• استقرار التصميم على المدى الطويل

في السيناريوهات التي يكون فيها التوفر وتجميد التصميم على المدى الطويل أكثر أهمية من الأداء المتطور ، يعد هذا الجهاز مرشحًا قويًا.بمجرد أن يتم التحقق من صحة المنطق وملف التكوين لأسفل ، يمكن أن يظل النظام بأكمله دون تغيير لسنوات ، وحتى عقود.هذه فائدة كبيرة في الطيران والنقل والتطبيقات العسكرية حيث يكون استئصال الأجزاء الجديدة باهظة الثمن أو غير عملي.

EPF6016ATC144-2N أبعاد التغليف

نوع الحزمة: TQFP-144 (حزمة مسطحة رباعية رقيقة)

حجم الجسم: 20 مم × 20 مم

دبوس الملعب: 0.5 مم

عدد الدبوس: 144 دبابيس

ارتفاع الحزمة: 1.0 مم

نوع الإطار الرصاص: Gull-Wing يؤدي على جميع الأطراف الأربعة

نوع التثبيت: سطح السطح (SMT)

EPF6016ATC144-2N الشركة المصنعة

تم تصنيع EPF6016ATC144-2N في الأصل شركة Altera، رائد في تطوير صفائف بوابة قابلة للبرمجة (FPGAs).في عام 2015 ، تم الحصول على Altera بواسطة شركة إنتل، والجهاز الآن مدرج رسميًا في إطار مجموعة Intel القابلة للبرمجة ، والتي تدير وتدعم خطوط إنتاج FPGA القديمة.على الرغم من أن EPF6016ATC144-2N جزء من عائلة متوقفة ، إلا أن Intel تظل الشركة المصنعة الرسمية والوصي في هذا الجهاز ، والحفاظ على الوثائق ، والدعم المؤرشفة ، وإشعارات دورة الحياة بموجب العلامة التجارية Intel.

خاتمة

EPF6016ATC144-2N هو FPGA مرنة ويمكن الاعتماد عليها للعديد من المشاريع المختلفة.إنه يوفر قدرًا كبيرًا من الطاقة المنطقية ، والعديد من دبابيس الإدخال/الإخراج ، وتحديثات سهلة في النظام.يدعم تصميمه أنظمة الجهد المختلط ، وحركة البيانات السريعة ، وإعادة البرمجة دون إزالتها من لوحة.غالبًا ما يتم استخدامه في أشياء مثل أنظمة التحكم ومعالجة الإشارات وروابط الاتصال ومعدات الاختبار.بدعم قوي ، وتوافر طويل ، والتعبئة البسيطة ، يظل خيارًا ذكيًا يحتاج إلى حل فعال ومستقر من حيث التكلفة.

ورقة البيانات pdf

EPF6016ATC144-2N أوراق البيانات:

معلومات عنا

ALLELCO LIMITED

قراءة المزيد

تحقيق سريع

الرجاء إرسال استفسار ، وسوف نرد على الفور.

أسئلة مكررة [FAQ]

1. ما هي الأدوات التي أحتاجها لبرمجة EPF6016ATC144-2N اليوم؟

يمكنك استخدام برنامج Intel Legacy Quartus II أو Max+Plus II للتطوير والتجميع.للبرمجة ، تظل أدوات مثل كابل USB-Blaster ومبرمج Quartus متوافقة مع التكوين.

2. هل EPF6016ATC144-2N مناسب لركضات الإنتاج الصغيرة أو النماذج الأولية؟

نعم.تجعل حزمة TQFP-144 من السهل النموذج الأولي دون الحاجة إلى أدوات التجميع المتقدمة.كما أنه مثالي للإنتاج على نطاق صغير حيث هناك حاجة إلى منخفضة التكلفة والمرونة.

3. كيف تقارن EPF6016ATC144-2N بأحدث FPGAs من حيث الأداء؟

على الرغم من أنها ليست غنية بالميزات مثل FPGAs المتطورة الحديثة ، فإن EPF6016ATC144-2N يوفر أداءً يمكن الاعتماد عليه لتعقيد المنطق المعتدل مع انخفاض استهلاك الطاقة والتكامل الأكثر بساطة ، مما يجعله فعالًا من حيث التكلفة للعديد من التطبيقات.

4. هل من الآمن أن تنقلب الساخنة على EPF6016ATC144-2N في الأنظمة الحية؟

نعم.يدعم FPGA مقبس الساخن لأنظمة 3.3 فولت ، مما يسمح بإدراجه أو إزالته دون تشغيل لوحة المضيف ، وهو مثالي للخدمة الميدانية أو تصميمات الأجهزة المعيارية.

5. لماذا يجب أن أختار EPF6016ATC144-2N على حلول ASIC أو CPLD المخصصة؟

يوفر EPF6016ATC144-2N دورات تطوير أسرع ، وإعادة برمجة الميدان ، وخفض التكلفة المقدمة مقارنة بـ ASIC.بالمقارنة مع CPLDS ، فإنه يوفر المزيد من السعة المنطقية والتوجيه المرن ، وهو مثالي للتصميمات القابلة للتطوير والمتطورة.

LC5768MC-75F256C CPLD: الميزات والمواصفات والمزايا والتطبيقات

على 10/07/2025

البدء مع MC7447AHX1000NB

على 10/07/2025

الوظائف الشعبية

-

أجهزة الكمبيوتر المعقدة لتعليمات التعليمات: كيف غيرت الحوسبة؟

على 19/04/8000 147781

-

usb-c pinout والميزات

على 19/04/2000 112052

-

باستخدام بدائل المحاكاة الموحدة Xilinx: دليل شامل لتصميم ومحاكاة FPGA

على 19/04/1600 111352

-

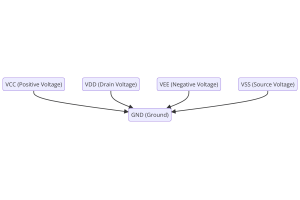

جهد مصدر الطاقة في الإلكترونيات: معنى VCC، VDD، VEE، VSS، وGND

على 19/04/0400 83808

-

دليل موصل RJ45: pinout ، الأسلاك ، أنواع الكابلات ، والاستخدامات

على 01/01/1970 79616

-

الدليل النهائي لرموز الألوان السلكية في الأنظمة الكهربائية الحديثة

الطريقة التي تستخدمها أنظمةنا الكهربائية بالألوان ليست فقط للمظهر.يشير كل لون سلك الآن إلى وظيفة محددة ، مما يسهل تحديد المكونات الكهربائية والتعامل معها بشكل صحيح أثناء التثبيت والصيانة.هذا لا يسر...على 01/01/1970 66992

-

دليل Purge Valve: الوظيفة والأعراض والاختبار والاستبدال لأداء المحرك الأمثل

يعد Purge Valve جزءًا رئيسيًا من نظام السيارة الذي يساعد في الحفاظ على نظافة الهواء من خلال إدارة أبخرة الوقود قبل أن يتمكنوا من الهروب إلى الجو.هذا لا يساعد البيئة فقط عن طريق تقليل التلوث ولكن أي...على 01/01/1970 63117

-

الجودة (س) العامل: المعادلات والتطبيقات

يعد عامل الجودة ، أو "Q" مهمًا عند التحقق من مدى عمل المحاثات والراتين في الأنظمة الإلكترونية التي تستخدم ترددات الراديو (RF).يقيس "Q" مدى تقليل الدائرة إلى تقليل فقدان الطاقة وتؤثر على نطاق التردد...على 01/01/1970 63055

-

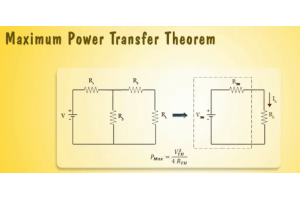

تحقيق ذروة أداء مع أقصى نظرية نقل الطاقة

تشرح نظرية نقل الطاقة القصوى كيف تتدفق الطاقة من مصدر ، مثل البطارية أو المولد ، إلى الحمل المتصل.يوضح الحالة الدقيقة التي يتلقى فيها الحمل أكثر الطاقة.تغطي هذه المقالة ما تعنيه النظرية ، وكيف تعمل...على 01/01/1970 54097

-

مواصفات البطارية A23 وتوافقها

بطارية A23 عبارة عن بطارية صغيرة على شكل أسطوانة مع جهد عالي.يُطلق عليه أيضًا 23a أو 23ae أو Mn21 ، ويتم تشغيله بسرعة 12 فولت وأعلى بكثير من بطاريات AA أو AAA.تصميمه الخاص يجعلها مثالية لل...على 01/01/1970 52204