EPM7256AETC144-10N CPLD: ورقة البيانات والمواصفات والتطبيقات ودليل البرمجة

EPM7256AETC144-10N هو جهاز منطقي قابل للبرمجة (CPLD) من سلسلة MAX® 7000A من Intel.تم تصميم هذه الشريحة للأداء السريع ، حيث تصل إلى 172.4 ميجاهرتز مع تأخير 10 نانو ثانية.يشرح هذا الدليل كل شيء عن هذا CPLD ، بما في ذلك ميزاته ومواصفاته واستخداماته وكيفية برمجته وتخطيطه.إذا كنت بحاجة إلى شريحة موثوقة وقابلة للبرمجة للدوائر الرقمية ، فستساعدك هذه المقالة على فهم كيفية عملها.كتالوج

EPM7256AETC144-10N الوصف

ال EPM7256AETC144-10N هو CPLD عالي الأداء من سلسلة MAX® 7000A Intel ، مصممة خصيصًا لمهام تكامل المنطق.يضم هذا الجهاز 256 من macrocells وحوالي 5000 بوابة قابلة للاستخدام ، مما يسهل مرونة تصميم كبيرة وفائدة في البيئات الرقمية المعقدة.تعمل بتردد أقصى قدرها 172.4 ميغاهيرتز مع تأخير انتشار قدره 5.5 نانو ثانية فقط ، وهو مصمم للتشغيل السريع.تم تصميمه مع جهد تشغيل 3.3 فولت وتعبئته في حزمة مسطحة رباعية رقيقة من 144 دبوس (TQFP) ، يدعم EPM7256AETC144-10N متطلبات تصميم المنطق القوية.تستخدم EPM7256AETC144-10N ذاكرة التكوين غير المتقلبة المستندة إلى EEPROM ، مما يتيح التخزين الدائم لبيانات البرمجة.توفر هذه الميزة ، بالإضافة إلى قابلية البرمجة داخل النظام عبر واجهة JTAG ، سهولة في التحديثات وإعادة البرمجة الميدانية ، وتعزيز قابلية الاستخدام على المدى الطويل دون الحاجة إلى إعادة التشكيل المادي أو الاستبدال.

قم بتأمين مشاريعك بتكنولوجيا موثوقة ومؤسسة ميدانية من خلال وضع طلبك الأكبر للحصول على EPM7256AETC144-10N معنا اليوم وضمان أن يكون لديك حل CPLD قوي.

EPM7256AETC144-10N CAD نماذج

EPM7256AETC144-10N الرمز

EPM7256AETC144-10N بصمة

EPM7256AETC144-10N 3D نموذج

EPM7256AETC144-10N

macrocells:تم تجهيز هذا الجهاز بـ 256 macrocells.Macrocells هي مكونات المنطق القابلة للتكوين التي تسمح لـ CPLD بإجراء وظائف منطقية مختلفة.

البوابات القابلة للاستخدام:يوفر ما يقرب من 5000 بوابة قابلة للاستخدام.يشير هذا إلى كمية مكافئة للبوابات المنطقية الأساسية (مثل ، أو ، أو لا) التي يمكن تكوينها داخل الجهاز.

دبابيس I/O:يتميز CPLD 120 دبابيس إدخال/إخراج ، والتي تسمح بتوصيل واسع النطاق مع أجزاء أخرى من التصميم الإلكتروني للمستخدم.

تأخير الانتشار (TPD):الحد الأقصى لتأخير الانتشار هو 10 نانو ثانية ، ويحدد السرعة التي يمكن لـ CPLD بمعالجة إشارات الإدخال وإنتاج المخرجات.

تردد التشغيل:يمكن أن تعمل بترددات تصل إلى 95.2 ميغاهيرتز ، والتي تحدد السرعة التي يمكن للجهاز تنفيذها عمليات المنطق.

جهد العرض:يعمل الجهاز عند جهد إمداد 3.3 فولت ، ويحاذا مع مستويات المنطق الرقمية المنخفضة الجهد المنخفضة.

طَرد:إنه يأتي في حزمة مسطحة رباعية رقيقة من 144 دبوسًا (TQFP) ، وهو نوع حزمة مضغوط مواتية لتقليل المساحة المطلوبة على لوحات الدوائر المطبوعة.

نطاق درجة حرارة التشغيل:يتراوح نطاق درجة حرارة التشغيل من 0 درجة مئوية إلى 70 درجة مئوية ، مما يضمن أداء موثوق به على نطاق واسع من الظروف البيئية.

قابلية البرمجة في النظام:يدعم CPLD قابلية البرمجة في النظام عبر IEEE STD.1149.1 واجهة مجموعة الاختبار المشتركة (JTAG) ، مما يتيح البرمجة وإعادة برمجة الجهاز المنطقي ضمن تكوين الأجهزة النهائية.

EPM7256AETC144-10N مخطط كتلة

ال EPM7256AETC144-10N هو جهاز منطقي قابل للبرمجة معقد (CPLD) مع أربعة كتل صفيف المنطق (مختبرات) ، كل يحتوي على 16 macrocells ، ويبلغ مجموعها 64 macrocells.تتعامل هذه macrocells مع كل من المنطق التوافقي والتسلسل ، مما يجعل الجهاز مرنًا لمختلف تطبيقات المنطق الرقمي.في وسط CPLD هو صفيف التوصيل القابل للبرمجة (PIA)الذي يربط جميع المعامل ، وضمان توجيه الإشارة الفعال.يتواصل كل مختبر مع PIA باستخدام 36 خطًا ربطًا ، مما يسمح بمشاركة الإشارات ومعالجتها بكفاءة.يتميز الجهاز بمكتلات التحكم I/O على كل جانب ، ودعم 2 إلى 16 دبابيس I/O لكل مختبر.تساعد هذه الكتل في إدارة وظائف الإدخال والإخراج ، وتوصيل CPLD بالدوائر الخارجية.تساعد إشارات التحكم مثل الساعات العالمية (GCLK1 و GCLK2) والإخراج (OE1) و Reset Global (GCLRN) على مزامنة عمليات المنطق عبر الجهاز.بالإضافة إلى ذلك ، تدير البوابات المنطقية الإشارات على مدار الساعة وإعادة ضبطها ، مما يضمن التشغيل السلس.تم تصميم هذا CPLD للمعالجة المنطقية عالية السرعة ، مما يوفر برمجة ، وتوجيه إشارة فعال ، والتحكم في الإدخال/الإخراج الموثوق به ، مما يجعلها مناسبة للأنظمة المضمنة والاتصالات والأتمتة الصناعية.

EPM7256AETC144-10N المواصفات

|

يكتب |

المعلمة |

|

الشركة المصنعة |

Altera/Intel |

|

مسلسل |

Max® 7000a |

|

التغليف |

صينية |

|

حالة الجزء |

عفا عليها الزمن |

|

نوع قابل للبرمجة |

في النظام قابل للبرمجة |

|

تأخير وقت TPD (1) كحد أقصى |

10 ns |

|

إمداد الجهد - داخلي |

3V ~ 3.6V |

|

عدد العناصر/الكتل المنطقية |

16 |

|

عدد macrocells |

256 |

|

عدد البوابات |

5000 |

|

عدد i/o |

120 |

|

درجة حرارة التشغيل |

0 درجة مئوية ~ 70 درجة مئوية (TA) |

|

نوع التثبيت |

جبل السطح |

|

حزمة / حالة |

144-LQFP |

|

حزمة جهاز المورد |

144-TQFP (20x20) |

|

رقم المنتج الأساسي |

EPM7256 |

EPM7256AETC144-10N تطبيقات

الذكاء الاصطناعي

يتم استخدام هذا CPLD في مسرعات أجهزة الذكاء الاصطناعي للتعامل مع الحسابات المعقدة المطلوبة لمعالجة خوارزميات الذكاء الاصطناعى بكفاءة ، مما يعزز كل من السرعة والموثوقية في تطبيقات الذكاء الاصطناعي.

تقنية 5G

في عالم الاتصالات 5G ، يعد EPM7256AETC144-10N أفضل لبروتوكولات معالجة الإشارات وإدارة بروتوكولات الاتصال.تسهل عمليات المنطق عالية السرعة الخاصة بها المعالجة السريعة اللازمة في الجيل القادم من الأنظمة اللاسلكية.

الحوسبة السحابية

ضمن مراكز البيانات ، يحسن هذا الجهاز إمكانات المعالجة ، ويعمل كمكون لإدارة كميات كبيرة من البيانات والحسابات المعقدة ، ودعم البنية التحتية للخدمات السحابية.

إلكترونيات المستهلك

يجد CPLD تطبيقات في الإلكترونيات الاستهلاكية مثل أجهزة التلفزيون ووحدات التحكم في الألعاب ، حيث تؤدي وظائف منطقية مخصصة تعزز وظائف الجهاز والخبرة.

التكنولوجيا اللاسلكية

يتم استخدامه في أجهزة الاتصال اللاسلكية لتعديل الإشارات وتوضيحها ، مما يضمن التواصل الفعال والفعال في أجهزة مثل أجهزة التوجيه والمودم الخلوي.

السيطرة الصناعية

هذا الجهاز جزء لا يتجزأ من أنظمة الأتمتة في الإعدادات الصناعية ، حيث يتحكم في الآلات ويدير العمليات ، والمساهمة في زيادة الإنتاجية والسلامة.

إنترنت الأشياء (IoT)

في أجهزة إنترنت الأشياء ، تدير EPM7256AETC144-10N مهام معالجة البيانات والاتصالات ، وهي رائعة للتشغيل السلس للأجهزة المتصلة في المنازل والصناعات الذكية.

المعدات الطبية

يتم تطبيق CPLD في الأجهزة الطبية للمهام مثل الحصول على البيانات ومعالجة الإشارات ، ولعب دور في موثوقية وكفاءة التشخيص الطبي ومعدات العلاج.

EPM7256AETC144-10N أجزاء مماثلة

EPM7256AETC144-10N مزايا

كثافة المنطق العالية

يحزم هذا الجهاز 256 Macrocells وحوالي 5000 بوابة قابلة للاستخدام ، مما يتيح تنفيذ دوائر منطقية معقدة داخل شريحة واحدة.تسهل هذه الكثافة المنطقية العالية تصميمات أكثر تكاملاً وضغوطًا ، مما يقلل من عدد المكونات الإجمالية وتبسيط تخطيطات اللوح.

قابلية البرمجة في النظام (ISP)

يضم قابلية البرمجة في النظام عبر IEEE Std.1149.1 واجهة JTAG ، تسمح EPM7256AETC144-10N ببرمجة سهلة وإعادة البرمجة مباشرة داخل الدائرة.هذه القدرة لا تقدر بثمن بالنسبة للنماذج الأولية السريعة والتصميم التكراري ، مما يتيح إجراء تعديلات دون الحاجة إلى استبدال الشريحة.

تأخير انتشار سريع

مع وجود أقصى قدر من التأخير في الانتشار البالغ 10 نانو ثانية ، يضمن هذا CPLD المعالجة السريعة للمدخلات والمخرجات للتطبيقات التي تتطلب معالجة البيانات عالية السرعة والاستجابات في الوقت المناسب ، مثل معالجة الفيديو وأنظمة تداول التردد العالي.

استهلاك الطاقة المنخفض

تعمل على جهد إمداد 3.3 فولت ، تم تحسين EPM7256AETC144-10N لكفاءة الطاقة.يعد استهلاك الطاقة المنخفض هذا مفيدًا في الأجهزة المحمولة والبطارية التي تعمل بالبطاريات ، حيث تعد إدارة الطاقة جيدة لتمديد العمر التشغيلي.

قدرات I/O شاملة

تم تجهيز الجهاز بـ 120 دبابيس I/O ، مما يوفر خيارات اتصال واسعة النطاق.يتيح ذلك التواصل المرن مع مجموعة واسعة من الأجهزة الطرفية ومكونات النظام الأخرى ، مما يجعله قابلاً للتكيف إلى حد كبير مع بيئات متعددة الأجهزة المعقدة.

تخزين التكوين غير المتطابق

بفضل ذاكرتها المستندة إلى EEPROM ، تحتفظ CPLD بإعدادات التكوين الخاصة بها حتى بعد إيقاف تشغيل الطاقة ، مما يضمن أن وظائف الجهاز ثابتة عبر دورات الطاقة.هناك حاجة إلى هذه الميزة للتطبيقات التي تتطلب أداءً يمكن الاعتماد عليه على المدى الطويل دون الحاجة إلى إعادة التشكيل المتكرر.

EPM7256AETC144-10N خطوات البرمجة

يتضمن برمجة جهاز EPM7256AETC144-10N عملية برمجة ستة مراحل (ISP):

1. أدخل ISP: هذه الخطوة تتأكد من أن أجزاء الإدخال والإخراج من الجهاز من الاستخدام العادي إلى وضع البرمجة بسلاسة.يستغرق حوالي 1 مللي ثانية.

2. تحقق من المعرف: قبل بدء البرمجة ، يتحقق الجهاز من معرفه الخاص.هذه الخطوة سريعة جدا.

3. المسح بالجملة: هذا يمسح جميع البيانات السابقة من الجهاز.يقوم بذلك عن طريق تلقي أمر لمحو كل شيء ثم انتظار 100 ميلي ثانية للتأكد من محو كل شيء.

4. البرنامج: هذا هو المكان الذي يتم فيه وضع البيانات الجديدة في الجهاز.لكل جزء من البيانات ، يتم إرساله إلى العنوان الصحيح في الجهاز ، ثم نبض خاص يتأكد من تخزينه بشكل صحيح.

5. تحقق من: بعد البرمجة ، يتحقق الجهاز إذا تم تخزين جميع البيانات بشكل صحيح من خلال قراءتها مرة أخرى ومقارنتها بما يجب أن يكون.

6. الخروج من ISP: تقوم هذه الخطوة بتبديل الجهاز مرة أخرى من وضع البرمجة إلى وضع الاستخدام العادي.كما يستغرق حوالي 1 مللي ثانية.

يعتمد إجمالي الوقت اللازم للبرمجة على المدة التي تستغرقها كل نبضة ومدى سرعة الانتقال إلى البيانات والخروج من الجهاز ، والتي تتأثر بسرعة ساعة البرمجة ومقدار البيانات الموجودة.قد تستغرق الأجهزة المختلفة كميات مختلفة من الوقت لأن لديها كميات مختلفة من الذاكرة للبرنامج.

EPM7256AETC144-10N الرسم التخطيطي للبرق

يوضح الرسم البياني مخطط حزمة EPM7256AETC144-10N وترقيم الدبوس.هذه الشريحة تأتي في أ TQFP-144 (حزمة مسطحة رفيعة مع 144 دبابيس)، وهذا يعني أنه يحتوي على عائق جيد يؤدي على جميع الجوانب الأربعة.يتميز موقع PIN 1 بنقطة صغيرة ، وزيادة أرقام الدبوس في اتجاه عقارب الساعة حول الحزمة.دبابيس مرجعية رئيسية مثل PIN 1 ، PIN 37 ، PIN 73 ، و PIN 109 مساعدة في الاتجاه أثناء تجميع ثنائي الفينيل متعدد الكلور.تحدد أبعاد الخطوط العريضة الحجم الفعلي للشريحة لضمان تركيب ثنائي الفينيل متعدد الكلور المناسب.يسمح ترتيب Pinout بتوجيه إشارة فعال ، مما يجعله مناسبًا للتطبيقات المنطقية المعقدة.يعد EPM7256AE جزءًا من سلسلة MAX 7000A CPLD ، والتي تضم 256 من قابلية البرمجة في النظام.تشير اللاحقة -10N إلى درجة السرعة 10 NS وحزمة خالية من الرصاص.

EPM7256AETC144-10N الشركة المصنعة

EPM7256AETC144-10N هو جهاز منطقي قابل للبرمجة (CPLD) تم تطويره في الأصل بواسطة Altera Corporation ، والذي تم الحصول عليه لاحقًا بواسطة شركة إنتل في عام 2015. منذ عملية الاستحواذ ، أصبحت Intel الشركة المصنعة الرسمية لخطوط إنتاج FPGA و CPLD التابعة لـ Altera ، بما في ذلك سلسلة MAX® 7000A ، والتي ينتمي إليها هذا الجهاز.تم تصميم EPM7256AETC144-10N للتطبيقات عالية الأداء ، منخفضة الطاقة ، ودعم قابلية البرمجة في النظام (ISP) عبر JTAG (IEEE 1149.1).على الرغم من أن Intel ورثت تقنية CPLD من Altera ، فقد تم إيقاف هذا الجهاز منذ ذلك الحين وتم تصنيفه الآن على أنه قديم ، مما يعني أن Intel لم تعد تنتجها أو تدعمها في التصنيع النشط.

خاتمة

EPM7256AETC144-10N هو CPLD قوي ومرن يستخدم في AI و 5G والحوسبة السحابية والآلات الصناعية وإنترنت الأشياء والأجهزة الطبية.يعالج البيانات بسرعة ، ويستخدم القليل من الطاقة ، ويسمح بإعادة البرمجة السهلة دون إزالتها من الدائرة.لا يزال مفيدًا للتصميمات القديمة التي تحتاج إلى منطق قابل للبرمجة بأداء مستقر.سواء كنت تعمل مع هذا CPLD أو تبحث عن بدائل مماثلة ، فإن فهم تصميمه وبرمجته وفوائده يمكن أن يساعدك على الاستفادة من ذلك في التطبيقات الرقمية عالية السرعة.

ورقة البيانات pdf

EPM7256AETC144-10N أوراق البيانات:

معلومات عنا

ALLELCO LIMITED

قراءة المزيد

تحقيق سريع

الرجاء إرسال استفسار ، وسوف نرد على الفور.

أسئلة مكررة [FAQ]

1. كم عدد العناصر المنطقية أو البوابات التي يمكن لمقبض EPM7256AETC144-10N؟

يوفر EPM7256AETC144-10N 256 من الكروسيل وحوالي 5000 بوابة قابلة للاستخدام ، مما يسمح بتطبيقات المنطق المعقدة بشكل معتدل.

2. كيف يمكنني برمجة EPM7256AETC144-10N ، وما هي الأدوات التي أحتاجها؟

تدعم EPM7256AETC144-10N قابلية البرنامج (ISP) عبر واجهة JTAG (IEEE 1149.1).ستحتاج إلى برنامج Altera USB-Blaster أو Intel Quartus Prime لكتابة بيانات التكوين إلى الشريحة.

3. ما هي الاختلافات بين EPM7256AETC144-10N و EPM7256AETC144-7؟

الفرق الأساسي هو السرعة.لدى EPM7256AETC144-10N تأخير انتشار أقصى قدر من 10 نانو ثانية ، في حين أن EPM7256AETC144-7 لديه تأخير أسرع 7 نانو ثانية للتطبيقات ذات السرعة العالية.يشترك كلا الجهازين في نفس الحزمة ، وعدد الإدخال/الإخراج ، وهيكل macrocell.

4. هل يتطلب EPM7256AETC144-10N مذبذب خارجي؟

لا ، لا يتطلب CPLD نفسه مذبذبًا خارجيًا ، لكنه يدعم مدخلات الساعة الخارجية.إذا كان التصميم الخاص بك يحتاج إلى توقيت دقيق ، فيمكن استخدام إشارة الساعة الخارجية لدفع عملياتها المنطقية.

5. ما الذي يجعل EPM7256AETC144-10N يختلف عن CPLDs الأخرى في سلسلة MAX 7000A؟

يبرز هذا CPLD بسبب أدائه عالي السرعة (تأخير انتشار 10 نانو ثانية) ، و 256 Macrocells ، و 5000 بوابة قابلة للاستخدام ، مما يجعلها مثالية لتصميمات المنطق المعقدة.كما يدعم قابلية البرنامج داخل النظام (ISP) عبر JTAG ، على عكس بعض النماذج القديمة.

MPC8245LZU300D المعالج: ورقة البيانات والميزات والتطبيقات والمواصفات

على 13/03/2025

دليل بسيط لبطاريات L1154 للاستخدام اليومي

على 13/03/2025

الوظائف الشعبية

-

أجهزة الكمبيوتر المعقدة لتعليمات التعليمات: كيف غيرت الحوسبة؟

على 19/04/8000 147782

-

usb-c pinout والميزات

على 19/04/2000 112065

-

باستخدام بدائل المحاكاة الموحدة Xilinx: دليل شامل لتصميم ومحاكاة FPGA

على 19/04/1600 111352

-

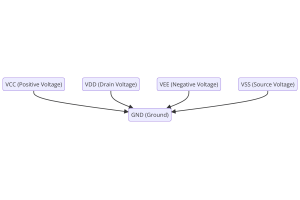

جهد مصدر الطاقة في الإلكترونيات: معنى VCC، VDD، VEE، VSS، وGND

على 19/04/0400 83819

-

دليل موصل RJ45: pinout ، الأسلاك ، أنواع الكابلات ، والاستخدامات

على 01/01/1970 79639

-

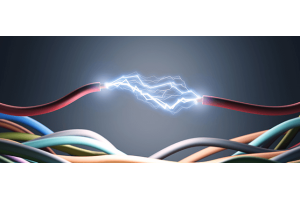

الدليل النهائي لرموز الألوان السلكية في الأنظمة الكهربائية الحديثة

الطريقة التي تستخدمها أنظمةنا الكهربائية بالألوان ليست فقط للمظهر.يشير كل لون سلك الآن إلى وظيفة محددة ، مما يسهل تحديد المكونات الكهربائية والتعامل معها بشكل صحيح أثناء التثبيت والصيانة.هذا لا يسر...على 01/01/1970 67000

-

دليل Purge Valve: الوظيفة والأعراض والاختبار والاستبدال لأداء المحرك الأمثل

يعد Purge Valve جزءًا رئيسيًا من نظام السيارة الذي يساعد في الحفاظ على نظافة الهواء من خلال إدارة أبخرة الوقود قبل أن يتمكنوا من الهروب إلى الجو.هذا لا يساعد البيئة فقط عن طريق تقليل التلوث ولكن أي...على 01/01/1970 63125

-

الجودة (س) العامل: المعادلات والتطبيقات

يعد عامل الجودة ، أو "Q" مهمًا عند التحقق من مدى عمل المحاثات والراتين في الأنظمة الإلكترونية التي تستخدم ترددات الراديو (RF).يقيس "Q" مدى تقليل الدائرة إلى تقليل فقدان الطاقة وتؤثر على نطاق التردد...على 01/01/1970 63064

-

تحقيق ذروة أداء مع أقصى نظرية نقل الطاقة

تشرح نظرية نقل الطاقة القصوى كيف تتدفق الطاقة من مصدر ، مثل البطارية أو المولد ، إلى الحمل المتصل.يوضح الحالة الدقيقة التي يتلقى فيها الحمل أكثر الطاقة.تغطي هذه المقالة ما تعنيه النظرية ، وكيف تعمل...على 01/01/1970 54097

-

مواصفات البطارية A23 وتوافقها

بطارية A23 عبارة عن بطارية صغيرة على شكل أسطوانة مع جهد عالي.يُطلق عليه أيضًا 23a أو 23ae أو Mn21 ، ويتم تشغيله بسرعة 12 فولت وأعلى بكثير من بطاريات AA أو AAA.تصميمه الخاص يجعلها مثالية لل...على 01/01/1970 52215