نظرة عامة على LFEC3E-3Q208C FPGA: الميزات والتطبيقات والبرمجة والمواصفات

في هذه المقالة ، ستتعرف على LFEC3E-3Q208C ، وهو FPGA من شعرية أشباه الموصلات.سترى ما هو عليه ، والميزات الرئيسية التي يقدمها ، ولماذا مفيدة للعديد من التصميمات متوسطة المدى.يمشي المحتوى أيضًا من خلال مواصفاته وتطبيقاته وعملية البرمجة خطوة بخطوة ، إلى جانب إيجابياتها وسلبياته وتفاصيل الشركة المصنعة.كتالوج

ما هو LFEC3E-3Q208C؟

ال LFEC3E-3Q208C عبارة عن مجموعة بوابة قابلة للبرمجة (FPGA) من حيث التكلفة من حيث التكلفة من أشباه الموصلات ، المصممة كجزء من عائلة Latticeec (الاقتصاد).تم تطوير هذه العائلة لتقديم حلول منطقية قابلة للبرمجة توازن بين القدرة على تحمل التكاليف مع أداء موثوق للتصميمات السائدة.داخل التسلسل الهرمي لشبكة Latticeec ، يقع في منتصف المدى ، حيث يوفر حوالي 3000 عنصر منطقي واستخدام فعال للطاقة ، وسد الفجوة بين أجهزة الدخول الأصغر والنماذج الأكبر والأكثر كثافة في الموارد.تؤكد سلسلة LatticeCP/EC الأوسع نطاقًا على القدرة على البرمجة منخفضة التكلفة وقابلية التوسع والمرونة عبر أحجام متعددة للأجهزة ، مع التركيز على الأداء القائم على الاقتصاد.

هل تبحث عن LFEC3E-3Q208C؟اتصل بنا للتحقق من الأسهم الحالية ، وتهمة المهلة ، والتسعير.

ميزات LFEC3E-3Q208C

• الموارد المنطقية

يدمج الجهاز حوالي 3100 عنصر منطقي منظم في 384 قطعة ، مما يمنحه سعة كافية للتصاميم متوسطة المدى.يجعل توازن الموارد هذا مناسبًا لمنطق التحكم ومعالجة الإشارات والتطبيقات المضمنة دون تكلفة مفرطة.

• I/O قابل للبرمجة

مع ما يصل إلى 145 دبابيس إدخال/إخراج قابلة للبرمجة ، فإنه يدعم مجموعة واسعة من خيارات الاتصال.تتوافق هذه الإدخال/OS مع معايير متعددة مثل LVCMOS و LVTTL و LVDs و PCI و SSTL ، مما يتيح تكامل النظام المرن.

• ذاكرة مضمنة

يشتمل FPGA على RAM المخصص للكتلة (EBR) وموارد ذاكرة الوصول العشوائي الموزعة ، مما يوفر تخزينًا فعالًا على الرقاقة.يسمح ذلك بتنفيذ بيانات التخزين المؤقت للبيانات أو طاولات البحث أو الذكريات المدمجة الصغيرة مباشرة داخل الجهاز.

• إدارة الساعة

إنه يتميز بما يصل إلى أربعة PLLs متكاملة ، مما يوفر تكاثر التردد ، والتقسيم ، وتحويل الطور.وهذا يتيح التحكم الدقيق في التوقيت والمزامنة للتصميمات عالية السرعة.

• دعم الذاكرة DDR

يتضمن الجهاز دعم الأجهزة لواجهات DDR ، قادرة على تشغيل DDR400 (200 ميغاهيرتز).هذا يجعل من العملي للتصميمات التي تتطلب الوصول الخارجي للذاكرة عالية السرعة.

• كفاءة الطاقة

تعمل مع الإمداد الأساسي 1.2 فولت ، يقلل FPGA من استهلاك طاقة النظام بشكل عام.يعد تصميم الطاقة المنخفضة مثاليًا للتطبيقات المحمولة أو الحساسة للطاقة.

• ميزات مستوى النظام

وظائف مدمجة مثل IEEE 1149.1 المسح الضوئي الحدودي ، تحليل المنطق على الرقاقة (ISPTRACY) ، وواجهة Flash SPI بتبسيط الاختبار وتصحيح الأخطاء.هذه الميزات تقلل من وقت التطوير وتحسن موثوقية التصميم.

• دعم التنمية

بدعم من جناح تصميم Isplever ، يستفيد الجهاز من التوليف الآلي ، والمكان والوقوف ، وأدوات التحقق.يمكنك أيضًا استخدام كتل IP ISPlevercore لتسريع الوظائف المشتركة وتقصير وقت السوق.

LatticeECP/EC العائلة المخطط

يوضح مخطط الكتلة لعائلة LatticeCP/EC (بما في ذلك LFEC3E-3Q208C) كيف تم بناء FPGA وكيفية عمل أجزائه معًا.يتم وضع خلايا الإدخال/الإخراج القابلة للبرمجة (الصور) حول الحواف لتوصيل الشريحة بالأجهزة الخارجية ، ودعم العديد من معايير الإشارة.في الداخل ، تتعامل الوحدات الوظيفية القابلة للبرمجة (PFUS) مع عمليات المنطق ، مع وجود بعضها على RAM المدمج للكتل المدمجة (EBR) لتخزين البيانات والبعض الآخر يركز فقط على المنطق.إدارة SYSCLOCK PLLS إدارة الإشارات على مدار الساعة بحيث يمكن للتصميم تشغيل بسرعة وتوقيت.يتيح لك منفذ SysConfig ومنفذ JTAG البرمجة واختبار وتصحيح FPGA بسهولة.يمنح هذا التصميم مرونة LFEC3E-3Q208C والأداء الموثوق والتكامل البسيط في التصميمات الحساسة للتكلفة.

Latticeecp/EC شريحة مخطط

الشريحة في عائلة Latticeecp/EC ، كما هو الحال في LFEC3E-3Q208C ، هي وحدة المنطق الأساسية التي تجمع بين LUT4 & Carry Clochs لأداء العمليات المنطقية والحساب.تتضمن كل شريحة أيضًا flip-flops/المزالج لتخزين البيانات وتمكين المنطق المتسلسل ، مع مضاعفة الإرسال لتوجيه إشارات مرونة إما من خلال السجلات أو مباشرة.هذا الهيكل مهم لأنه يمنح سرعة FPGA والمرونة والكفاءة للتعامل مع كل من التصميمات الرقمية البسيطة والمعقدة.يلخص الجدول التالي أوصاف إشارة الشريحة ، بما في ذلك وظائفها وأنواعها وأسماء الإشارات والأغراض.

|

وظيفة |

يكتب |

أسماء الإشارة |

وصف |

|

مدخل |

إشارة البيانات |

A0 ، B0 ، C0 ، D0 |

المدخلات إلى LUT4 |

|

مدخل |

إشارة البيانات |

A1 ، B1 ، C1 ، D1 |

المدخلات إلى LUT4 |

|

مدخل |

متعدد الأغراض |

M0 |

إدخال متعدد الأغراض |

|

مدخل |

متعدد الأغراض |

M1 |

إدخال متعدد الأغراض |

|

مدخل |

إشارة التحكم |

م |

تمكين الساعة |

|

مدخل |

إشارة التحكم |

LSR |

مجموعة/إعادة ضبط محلية |

|

مدخل |

إشارة التحكم |

CLK |

ساعة النظام |

|

مدخل |

إشارة inter-PFU |

fcin |

حمل سريع in¹ |

|

الإخراج |

إشارات البيانات |

F0 ، F1 |

LUT4 سجل الإخراج الإشارات الالتفافية |

|

الإخراج |

إشارات البيانات |

Q0 ، Q1 |

تسجيل المخرجات |

|

الإخراج |

إشارات البيانات |

ofx0 |

إخراج LUT5 MUX |

|

الإخراج |

إشارات البيانات |

ofx1 |

إخراج LUT6 ، LUT7 ، LUT8 2 MUX اعتمادًا على الشريحة |

|

الإخراج |

إشارة inter-PFU |

FCO |

بالنسبة للحق في PFU ، فإن سلسلة الحمل السريع |

مواصفات LFEC3E-3Q208C

|

يكتب |

المعلمة |

|

الشركة المصنعة |

شعرية أشباه الموصلات |

|

الجهد - العرض |

1.14V ~ 1.26V |

|

مجموع البتات الكبش |

56،320 |

|

حزمة جهاز المورد |

208-PQFP (28x28) |

|

مسلسل |

EC |

|

حزمة / حالة |

208-BFQFP |

|

طَرد |

صينية |

|

درجة حرارة التشغيل |

0 درجة مئوية ~ 85 درجة مئوية (TJ) |

|

عدد العناصر/الخلايا المنطقية |

3،100 |

|

عدد i/o |

145 |

|

نوع التثبيت |

جبل السطح |

|

رقم المنتج الأساسي |

LFEC3 |

تطبيقات LFEC3E-3Q208C

1. أنظمة التحكم المدمجة

إن LFEC3E-3Q208C مناسب تمامًا لوحدات التحكم المدمجة في الأجهزة والأتمتة الصناعية وبوابات IoT.تسمح كثافة المنطق المعتدلة وتصميمها منخفض التكلفة باستبدال منطق الوظيفة الثابتة بمرونة قابلة للبرمجة.هذا يجعل من السهل ترقية الأنظمة أو التكيف مع المعايير المتطورة دون إعادة تصميم الأجهزة.

2. تواصل ذاكرة DDR

بدعم مدمج لذاكرة DDR400 ، يمكن للجهاز إدارة التخزين المؤقت للبيانات أو التسجيل أو التخزين المؤقت في التطبيقات.هذه الميزة مفيدة في الأنظمة التي تكون فيها سرعة الذاكرة الخارجية مهمة ولكن أداء FPGA الكامل غير المطلوب.يستفيد الكثير من توازن السرعة والتكلفة وكفاءة الذاكرة.

3. تحويل I/O وتحويل البروتوكول

بفضل دعمها الواسع لمعايير I/O مثل LVCMOS و LVTTL و LVDs و PCI و SSTL ، فإن FPGA فعال في سد واجهات رقمية مختلفة.يمكن تكوينه لترجمة الإشارات بين الأنظمة الفرعية ، مما يجعلها ذات قيمة في تصميمات التكنولوجيا المختلطة.تساعد هذه المرونة على تمديد عمر الأجهزة الحالية عن طريق تمكين التوافق مع مكونات جديدة.

4.

يمكن للجهاز أيضًا أن يعمل في معدات الصناعية والبنية التحتية الحساسة للتكلفة حيث تكون الموثوقية والأداء المعتدل كافيين.إن دعمها للمسح الضوئي الحدودي ، وتصحيح الأخطاء على الرقاقة ، والتشغيل المنخفض الطاقة يجعلها مثالية للأنظمة التي تتطلب كفاءة وسهولة الصيانة.تشمل الأدوار النموذجية وحدات التحكم ووحدات الواجهة وأنظمة المراقبة.

LFEC3E-3Q208C أجزاء مماثلة

|

مواصفة |

LFEC3E-3Q208C |

LFEC3E-3Q208I |

LFEC3E-3QN208C |

LFEC3E-4Q208C |

LFEC1E-3Q208C

|

LFEC6E-3Q208C

|

|

العناصر المنطقية (LUTS) |

~ 3.1k |

~ 3.1k |

~ 3.1k |

~ 3.1k |

~ 1.5k |

~ 6.1k |

|

كتل المنطق |

384 |

384 |

384 |

384 |

192 |

768 |

|

كتلة كتلة مدمجة (EBR) |

~ 55 كيلو بايت |

~ 55 كيلو بايت |

~ 55 كيلو بايت |

~ 55 كيلو بايت |

~ 18 كيلو بايت |

~ 92 كيلو بايت |

|

الحد الأقصى لتكرار التشغيل |

~ 340 ميغاهيرتز |

~ 340 ميغاهيرتز |

~ 340 ميغاهيرتز |

~ 340 ميغاهيرتز |

~ 300 ميغاهيرتز |

~ 340 ميغاهيرتز |

|

I/O Count |

145 |

145 |

145 |

145 |

112 |

145 |

|

طَرد |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

208-PQFP |

|

الجهد الأساسي |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

|

نطاق درجة الحرارة |

0 درجة مئوية إلى +70 درجة مئوية |

-40 درجة مئوية إلى +85 درجة مئوية |

0 درجة مئوية إلى +70 درجة مئوية |

0 درجة مئوية إلى +70 درجة مئوية |

0 درجة مئوية إلى +70 درجة مئوية |

0 درجة مئوية إلى +70 درجة مئوية |

|

الامتثال / نوع الحزمة |

معيار |

صناعي |

خالية من الرصاص (QN) |

البديل (س) |

معيار |

معيار |

|

طلب |

منتصف الكثافة ، للأغراض العامة |

مثل LFEC3E ولكن الاستخدام الصناعي |

نفس LFEC3E ولكن متوافقة مع الحزمة |

نفس العائلة ، الهجرة السهلة |

خيار التكلفة منخفضة الكثافة |

ترقية عالية الكثافة |

LFEC3E-3Q208C خطوات البرمجة

قبل البدء في برمجة LFEC3E-3Q208C ، من المهم إعداد الأدوات الصحيحة وفهم تدفق التصميم إلى تكوين الجهاز.تبني كل خطوة على الخطوة السابقة ، لذا فإن الاهتمام الدقيق سيضمن عملية برمجة سلسة.

1. إعداد أجهزة البرمجة والبرامج

يمكنك البدء بتثبيت مبرمج Diamond الخاص بـ Lattice أو نظام ISPVM ، والتي تعد الأدوات الرسمية لهذا FPGA.بعد ذلك ، قم بإعداد كابل برمجة JTAG مثل HW-USBN-2B وتأكد من تثبيت برامج التشغيل بشكل صحيح.تضمن هذه الخطوة أن يكون جهاز الكمبيوتر الخاص بك جاهزًا للتواصل مع الجهاز المستهدف دون أخطاء اتصال.

2. تنفيذ التصميم الخاص بك في برنامج التطوير

بعد ذلك ، قم بإنشاء مشروع جديد في Lattice Diamond وحدد LFEC3E-3Q208C كجهاز مستهدف.يمكنك بعد ذلك إضافة ملفات مصدر Verilog أو VHDL ، وتطبيق تعيينات PIN ، وتحديد أي قيود توقيت.بمجرد الانتهاء من ذلك ، تقوم بتوليف التصميم ، وتنفيذ مكان وتجارة ، وأخيراً إنشاء ملف BitStream (.bit أو .jed) الذي سيتم استخدامه للبرمجة.

3. قم بإعداد اللوحة والاتصالات

الآن ، قم بتوصيل كابل JTAG بلوحة FPGA ، مع التأكد من أن الاتصال الأرضي آمن قبل إرفاق خطوط الإشارة.تأكد من أن المقاومات السحب والانسحاب في مكانها بشكل صحيح ، وخاصة على خطوط TCK وخطوط السحب المفتوح.إذا كانت اللوحة الخاصة بك تحتوي على دبابيس تحكم إضافية مثل Erase أو ISPEN ، فأنت بحاجة إلى تكوينها بشكل صحيح لمنع إعادة التعيينات العرضية أثناء البرمجة.

4. برمجة الجهاز

مع استعداد الأجهزة ، قم بتشغيل أداة البرمجة وحدد الكبل المتصل.قم بتحميل ملف BitStream الذي تم إنشاؤه واختر الوضع المناسب ، وعادة ما يكون JTAG ، اعتمادًا على الإعداد الخاص بك.ابدأ عملية البرمجة ، وستقوم الأداة بتكوين FPGA مع التحقق من كتابة البيانات بشكل صحيح.

5. تحقق من التكوين وتصحيحه

بعد البرمجة ، تحقق من دبابيس تم القيام بها أو init على لوحتك لتأكيد تكوين FPGA بنجاح.إذا لزم الأمر ، استخدم محلل منطق ISPTRACY أو ميزات المسح الحدودي لاختبار الوظائف والتحقق من صحة سلوك الإشارة.يمكنك تكرار دورة التصميم والبرمجة عند الحاجة إلى التغييرات ، مما يضمن تحسين مشروعك خطوة بخطوة.

LFEC3E-3Q208C مزايا وعيوب

المزايا

• انخفاض استهلاك الطاقة ، مناسب للتصاميم الحساسة للطاقة

• فعالة من حيث التكلفة مقارنة بـ FPGAs الرفيعة

• مجموعة أدوات بسيطة مع منحنى تعليمي أسهل

• مجال إعادة تكوين الحقل للحصول على التحديثات بعد النشر

• حزمة مضغوطة مع توازن جيد في الموارد

عيوب

• أداء محدود مقارنة بـ FPGAs الأكبر

• انخفاض سعة المنطق وقدرة الذاكرة من الأجهزة الراقية

• عدد أقل من نوى IP لجهة خارجية ودعم النظام الإيكولوجي

• تفتقر أدوات الأدوات إلى الميزات المتقدمة للبائعين الرئيسيين

• غير مناسب للواجهات عالية السرعة

LFEC3E-3Q208C أبعاد التغليف

|

يكتب |

المعلمة |

|

نوع الحزمة |

208-PQFP (حزمة مسطحة رباعية بلاستيكية) |

|

حجم الجسم |

28 مم × 28 مم |

|

يقذف |

0.5 مم |

|

ارتفاع الحزمة (الحد الأقصى) |

~ 3.4 مم |

|

عدد الرصاص |

208 دبابيس |

|

نمط الحزمة |

Leads Gull-Wing (Quad) |

|

نوع التثبيت |

جبل السطح |

|

رمز القضية |

BFQFP-208 |

|

حزمة المورد |

صينية |

LFEC3E-3Q208C الشركة المصنعة

يتم تصنيع LFEC3E-3Q208C بواسطة شعرية Semiconductor Corporation ، وهي شركة مقرها الولايات المتحدة مقرها في هيلزبورو ، أوريغون.تأسست Lattice في عام 1983 ، متخصصة في تطوير صفائف البوابة ذات الطاقة المنخفضة والفعالة من حيث التكلفة (FPGAs) والحلول ذات الصلة.تركز الشركة على تمكين التطبيقات في الاتصالات والحوسبة والإلكترونيات الاستهلاكية والأسواق الصناعية والسيارات.اشتهرت Lattice بابتكارها في الأجهزة القابلة للبرمجة الموفرة للطاقة ، وقد أنشأت نفسها كلاعب رئيسي في صناعة FPGA ، وخاصة بالنسبة للتصميمات التي تتطلب عوامل الشكل المدمجة ، وتقليل استهلاك الطاقة ، وموثوقية عالية.

خاتمة

يوفر LFEC3E-3Q208C مزيجًا جيدًا من التكلفة المنخفضة ، والاستخدام المنخفض للطاقة ، والمنطق والذاكرة الكافية للمشاريع متوسطة المدى.وهو يدعم العديد من معايير الإدخال/الإخراج ، ويحتوي على ذاكرة الوصول العشوائي المدمجة و PLLs ، ويمكنه العمل مع ذاكرة DDR400 ، مما يجعلها مفيدة للتحكم والواجهة والمهام الصناعية.البرمجة بسيطة مع أدوات شعرية ، وميزات التصحيح الإضافية تساعد في الاختبار.على الرغم من أنه لا يمكن أن يتطابق مع سرعة وسعة FPGAs الأكبر ، إلا أنها اختيار موثوق للتصميمات التي تحتاج إلى مرونة وكفاءة وأداء معقول.

ورقة البيانات pdf

LFEC3E-3Q208C أوراق البيانات:

معلومات عنا

ALLELCO LIMITED

قراءة المزيد

تحقيق سريع

الرجاء إرسال استفسار ، وسوف نرد على الفور.

أسئلة مكررة [FAQ]

1. هل يدعم LFEC3E-3Q208C واجهات عالية السرعة مثل PCIE أو Gigabit Ethernet؟

لا. تم تصميم LFEC3E-3Q208C للتطبيقات السائدة والحساسة للتكلفة ، لذلك لا يشمل أجهزة الإرسال والاستقبال التسلسلية عالية السرعة.إنه يركز بدلاً من ذلك على الواجهات المتوازية ودعم ذاكرة DDR.

2. هل يمكن إعادة برمجة LFEC3E-3Q208C بعد النشر؟

نعم.باعتبارها FPGA ، فإن LFEC3E-3Q208C قابلة لإعادة التكوين بالكامل ، مما يسمح بالتحديثات وتعديلات التصميم حتى بعد النشر.هذه المرونة تقلل من تكاليف الصيانة طويلة الأجل وتمتد دورات حياة المنتج.

3. كيف يتعامل LFEC3E-3Q208C مع تصحيح الأخطاء والاختبار؟

يدمج الجهاز مسح الحدود (IEEE 1149.1) ، وتحليل المنطق على الرقاقة (ISPTRACY) ، ودعم Flash SPI.هذه الأدوات المدمجة تبسيط تصحيح الأخطاء وتقليل الحاجة إلى أجهزة الاختبار الخارجي.

4. هل يمكن ل LFEC3E-3Q208C تمديد عمر أنظمة الأجهزة القديمة؟

نعم ، بفضل إمكانيات توافق الإدخال/الإخراج الواسعة وقدرات سد البروتوكول ، يمكن أن تتفاعل الأنظمة القديمة مع مكونات أحدث ، مما يساعد الشركات على تمديد فائدة الأجهزة الحالية.

5. ما هي أدوات البرمجة المطلوبة لـ LFEC3E-3Q208C؟

تتم برمجتها باستخدام برنامج Lattice’s Diamond Programmer أو ISPVM.تدعم هذه الأدوات إدخال التصميم ، وتوليد BitStream ، وتكوين الجهاز ، مما يجعل سير العمل مبسطًا.

AD73111lars: ورقة البيانات ، والميزات ، ودانوت ودليل البرمجة

على 28/08/2025

EPM1270F256C4N MAX II CPLD نظرة عامة: الميزات والمواصفات والتطبيقات

على 28/08/2025

الوظائف الشعبية

-

أجهزة الكمبيوتر المعقدة لتعليمات التعليمات: كيف غيرت الحوسبة؟

على 19/04/8000 147782

-

usb-c pinout والميزات

على 19/04/2000 112062

-

باستخدام بدائل المحاكاة الموحدة Xilinx: دليل شامل لتصميم ومحاكاة FPGA

على 19/04/1600 111352

-

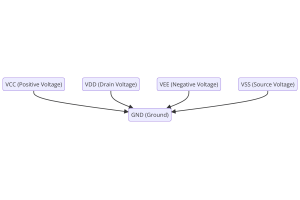

جهد مصدر الطاقة في الإلكترونيات: معنى VCC، VDD، VEE، VSS، وGND

على 19/04/0400 83819

-

دليل موصل RJ45: pinout ، الأسلاك ، أنواع الكابلات ، والاستخدامات

على 01/01/1970 79639

-

الدليل النهائي لرموز الألوان السلكية في الأنظمة الكهربائية الحديثة

الطريقة التي تستخدمها أنظمةنا الكهربائية بالألوان ليست فقط للمظهر.يشير كل لون سلك الآن إلى وظيفة محددة ، مما يسهل تحديد المكونات الكهربائية والتعامل معها بشكل صحيح أثناء التثبيت والصيانة.هذا لا يسر...على 01/01/1970 66999

-

دليل Purge Valve: الوظيفة والأعراض والاختبار والاستبدال لأداء المحرك الأمثل

يعد Purge Valve جزءًا رئيسيًا من نظام السيارة الذي يساعد في الحفاظ على نظافة الهواء من خلال إدارة أبخرة الوقود قبل أن يتمكنوا من الهروب إلى الجو.هذا لا يساعد البيئة فقط عن طريق تقليل التلوث ولكن أي...على 01/01/1970 63124

-

الجودة (س) العامل: المعادلات والتطبيقات

يعد عامل الجودة ، أو "Q" مهمًا عند التحقق من مدى عمل المحاثات والراتين في الأنظمة الإلكترونية التي تستخدم ترددات الراديو (RF).يقيس "Q" مدى تقليل الدائرة إلى تقليل فقدان الطاقة وتؤثر على نطاق التردد...على 01/01/1970 63062

-

تحقيق ذروة أداء مع أقصى نظرية نقل الطاقة

تشرح نظرية نقل الطاقة القصوى كيف تتدفق الطاقة من مصدر ، مثل البطارية أو المولد ، إلى الحمل المتصل.يوضح الحالة الدقيقة التي يتلقى فيها الحمل أكثر الطاقة.تغطي هذه المقالة ما تعنيه النظرية ، وكيف تعمل...على 01/01/1970 54097

-

مواصفات البطارية A23 وتوافقها

بطارية A23 عبارة عن بطارية صغيرة على شكل أسطوانة مع جهد عالي.يُطلق عليه أيضًا 23a أو 23ae أو Mn21 ، ويتم تشغيله بسرعة 12 فولت وأعلى بكثير من بطاريات AA أو AAA.تصميمه الخاص يجعلها مثالية لل...على 01/01/1970 52215