فهم d flip-flops: العمل والتطبيقات والمزايا

يشرح هذا الدليل ماهية A D Flip-Flop وكيف يعمل في الدوائر الرقمية.ستتعرف أيضًا على مزلاج 4 بت و 8 بت ، وكيفية عملها معًا ، ومكان استخدامها.يتضمن الدليل أمثلة على كيفية استخدام Dlip-Flops في أجهزة الكمبيوتر ، وجهاز التوقيت ، وأنظمة الاتصالات ، والأجهزة المدمجة.كما أنه يتحدث عن الجوانب الجيدة والسيئة لاستخدام dlip-flops في تصميماتك.كتالوج

ما هو D flip-flop؟

أ D Flip-Flop (اختصار لـ "البيانات" أو "التأخير" Flip-Flop) هي لبنة بناء أساسية في الإلكترونيات الرقمية المستخدمة لتخزين جزء واحد من المعلومات الثنائية.تعمل مع توقيت دقيق ، والتقاط البيانات والاحتفاظ بها فقط عندما تتغير إشارة الساعة عادةً على الحافة المتزايدة أو المتساقطة ، اعتمادًا على التصميم.عند وصول حافة الساعة ، يتم نقل القيمة الموجودة عند إدخال D (البيانات) إلى الإخراج ، المسمى Q. بعد ذلك ، يبقى الإخراج ثابتًا ، حتى إذا تغير إدخال البيانات ، حتى حافة الساعة الصالحة التالية.

الشكل 2. مخطط كتلة من الوجه d flop

هناك وضعان رئيسيان للتشغيل: متزامن وغير متزامن.في الوضع المتزامنيستجيب D Flip-Flop فقط لإشارات الساعة ، مما يضمن جميع أجزاء حالة تغيير الدائرة في انسجام تام.في الوضع غير المتزامن، يمكن للمدخلات الإضافية مثل الإعداد المسبق أو Clear تجاوز حالة الإخراج دون انتظار ساعة ، مما يتيح تهيئة سريعة أو إعادة ضبط.يحتوي Flip-Flop القياسي على مدخلان: البيانات (D) والساعة (CLK).أثناء حافة الساعة النشطة ، يلتقط قيمة الإدخال.عندما تكون الساعة غير نشطة ، فإن الإخراج ثابت.

كيف يعمل D flip-flop؟

يعمل D flip-flop ، المعروف عادة باسم "البيانات" أو "تأخير" flip-flop ، عن طريق المزامنة مع إشارة الساعة.آليتها الأساسية واضحة: إنها عينات قيمة الإدخال (د) عند انتقال ساعة محددة (عادةً حافة الارتفاع) والتحويلات التي تقدر إلى الإخراج (Q).يحتفظ الإخراج التكميلي (Q ′) بعكس Q. لأنه يستجيب فقط على حافة الساعة ، فإن D Flip-Flop هو عنصر تخزين يمكن الاعتماد عليه في الدوائر الرقمية.

الشكل 3. الدائرة المنطقية لـ D Flip-Flop

داخليًا ، غالبًا ما يتم تصميم Dlip-flops باستخدام تكوين بوابات منطقية في إعداد مزلاج ماجستير أو بوابات.يوضح الرسم البياني المقدم مزلاج DATED DATED DATED DATER ، والذي يعمل بشكل مشابه.المدخلات الرئيسية هي D (البيانات) و CLK (الساعة) ، والمخرجات هي Q و Q ′.عندما تكون CLK منخفضة ، تتجاهل الدائرة التغييرات في D ، مع الحفاظ على الإخراج الحالي.عندما يرتفع CLK ، يتم تحديثات الدائرة: إذا كانت D عالية ، يصبح Q مرتفعًا و Q ′ منخفضة ؛إذا كان D منخفضًا ، يصبح Q منخفضًا وتصبح Q ′ عالية.عندما تعود الساعة إلى أدنى مستوى ، يتم إغلاق الإخراج ، مع الحفاظ على حالته حتى نبض الساعة التالي.

يساعد جدول الحقيقة على توضيح هذا السلوك.عندما تكون الساعة غير نشطة أو لا تنتقل ، تمسك Q و Q ′ ثابتًا.على الحافة الصاعدة على مدار الساعة ، تأخذ Q القيمة الحالية لـ D (1 إذا كانت D عالية ، 0 إذا كانت D منخفضة) بينما يصبح Q ′ عكسه.تضمن هذه الاستجابة التي يتم تشغيلها على الحافة أن يتم تخزين البيانات الموجودة على حافة الساعة فقط ، مما يجعل Flip-Flop مستقرًا ومقاومًا للضوضاء أو التغيرات في المدخلات السريعة بين دورات الساعة.

جدول الحقيقة D Flip-Flop

|

CLK |

د |

س (الدولة التالية) |

س ' |

|

0 (منخفض) |

x |

س (دون تغيير) |

س ' |

|

↑ (الحافة الصاعدة) |

0 |

0 |

1 |

|

↑ (الحافة الصاعدة) |

1 |

1 |

0 |

|

1 (عالية ، لا حافة) |

x |

س (دون تغيير) |

س ' |

يوضح هذا الجدول أن D-Flip-Flop يقوم بتحديث إخراجه فقط على الحافة الصاعدة لإشارة الساعة التي تكون ، عندما تنتقل الساعة من منخفضة إلى عالية.في جميع الأوقات الأخرى ، يحافظ على إخراجها السابق ، وتجاهل أي تغييرات في إدخال البيانات.هذا السلوك الذي يمكن التنبؤ به ، حساس للحافة يجعل D flip-flop ذات قيمة في الأنظمة الرقمية حيث هناك حاجة إلى توقيت دقيق والتحكم في التسلسل.

باستخدام d flip-flops كمزلجة للبيانات

إلى جانب دورها في التحكم في التوقيت ، تعمل Dlip-Flops أيضًا كمساكن للبيانات.يحمل مزلاج البيانات قيمة إدخال في وقت محدد ويبقيه مستقرًا حتى الحاجة.هذا مفيد لعزل جزء من دائرة من آخر أو الحفاظ على البيانات أثناء المعالجة.يعمل المزلاج على أساس ساعة أو تمكين إشارة.عندما نشط ، فإنه يمرر الإدخال إلى الإخراج.عندما يكون غير نشط ، فإنه يغلق الإخراج الحالي في مكانه بغض النظر عن تغييرات الإدخال الإضافية.

أجهزة مثل 74LS74 (TTL) و 4042 (CMOs) هي أمثلة على الدوائر المتكاملة التي تحتوي على عوامل D-Flops متعددة.يمكن تجميع هذه الأجهزة لبناء سجلات الذاكرة أو وحدات التحكم.عندما يتم تشغيل العديد من التقلبات من خلال نفس إشارة التحكم ، يمكنهم تخزين قيم بيانات متعددة بت ، حيث تعمل كمكان مؤقت للمعلومات الرقمية.

4 بت مزلاج البيانات

الشكل 4. مزلاج البيانات 4 بت

يتكون مزلاج البيانات المكون من 4 بتات الموضحة في الرسم البياني من أربعة من نوع D-flops (المسمى FFA إلى FFD) ، كل مسؤول عن تخزين جزء واحد من المدخلات الثنائية 4 بت.تتم محاذاة هذه الوجهات المتقلبة بشكل متوازي وتحركها إشارة ساعة مشتركة ، مما يضمن التقاط جميع قيم الإدخال الأربعة الخاصة بها في وقت واحد على حافة الساعة.

يتلقى كل flip-flop بت إدخال منفصل (A و B و C و D) ويخرج القيمة المخزنة من خلال إخراج Q.عندما تكون نبض الساعة نشطًا ، يتم إغلاق قيم الإدخال الحالية في Flip-Flops.بمجرد الإغلاق ، تظل هذه القيم مستقرة ومتاحة عند الإخراج حتى وصول نبض الساعة التالي ، مع الاحتفاظ بفعالية أو "إغلاق" البيانات.

يمكّن هذا الهيكل المزلاج من العمل كوحدة تخزين البيانات المؤقتة ذات 4 بتات أو وحدة تخزين مؤقتة.إنها ذات قيمة في الأنظمة الرقمية التي تتطلب نقل البيانات المتزامن ، مثل وحدات المنطق الحسابي أو خطوط أنابيب التعليم أو حافلات العناوين.من خلال التقاط البيانات على إشارة الساعة المشتركة ، يضمن المزلاج تحكمًا دقيقًا عند تخزين البيانات ونقلها داخل الدائرة.

مزلاج بيانات شفاف

على عكس التقلبات التي يتم تشغيلها على الحافة ، فإن مزلاج شفاف يمرر بيانات الإدخال باستمرار إلى الإخراج طالما أن إشارة تمكينها نشطة.هذا السلوك يجعله مثاليًا للتطبيقات التي يلزم تدفق البيانات حتى يتجمد الأمر من الإخراج الحالي.

74LS373 هو مزلاج شفاف نموذجي.عندما تكون إشارة تمكينها عالية ، تتدفق البيانات من الإدخال إلى الإخراج في الوقت المناسب.عندما تنخفض إشارة التمكين ، يتم قفل المخرجات الحالية ، غير متأثرة بالتغيرات في الإدخال.

غالبًا ما يشتمل هذا النوع من المزلاج على مخرجات ثلاثية ، والتي يمكن أن تنفصل عن حافلة مشتركة عند عدم الحاجة إليها.هذا يمنع تعارض الإشارة ويمكن أجهزة متعددة من استخدام خطوط البيانات نفسها دون تداخل.المزالج الشفافة شائعة في دوائر الوصول إلى الذاكرة ، ومنطق الانعطاف ، والأنظمة التي تتطلب التقاط بيانات مؤقتة ولكن موثوقة.

8 بت مزلاج البيانات

الشكل 5. مزلاج البيانات 8 بت

يعتمد مزلاج البيانات المكون من 8 بت الموضحة أعلاه على مبادئ المزلاجات الأصغر من خلال دمج ثمانية نقاط متوازية ، قادرة على تخزين بايت كامل من البيانات من D0 إلى D7.يُرى هذا الإعداد بشكل شائع في دوائر متكاملة مثل 74LS373.يتم تجميع جميع Flops الثمانية داخل كتلة مزلاج ، والتي تلتقط بيانات الإدخال على الحافة الصاعدة لإشارة الساعة المشتركة (CLK).عندما تكون الساعة نشطة ويتم تأكيد خط ENABER (EN) ، يتم إغلاق قيم الإدخال الحالية وإتاحتها للإخراج.

متصلة بالمزلاج هي مرحلة إخراج ثلاثية الدولة.تتيح هذه الميزة للمخرجات (Q0 إلى Q7) إما قيادة خطوط البيانات أو إدخال حالة عالية الاستخدام (HI-Z) ، اعتمادًا على التحكم في تمكين الإخراج (OE).هذا السلوك الثلاثي مهم للأنظمة التي تتضمن حافلات بيانات مشتركة ، حيث يمنع تصادم الإشارات عندما تصل أجهزة متعددة إلى نفس الخطوط.تعتبر المزالج 8 بت كبيرة في الأنظمة الرقمية لمزامنة وتخزين البيانات على مستوى البايت مؤقتًا.غالبًا ما يتم العثور عليها في واجهات المعالجات الدقيقة ، وإغلاق عنوان الذاكرة ، وأجهزة الإدخال/الإخراج ، حيث تعمل كوسطاء بين مصادر البيانات السريعة ومكونات النظام أبطأ أو متزامنة.

تطبيقات d flip-flops

تعتبر Dlip-Flops مهمة جدًا في العديد من الأنظمة الرقمية.فهي تساعد في تتبع توقيت وتخزين البيانات بشكل صحيح ، وهو أمر مفيد لأشياء مثل الاحتفاظ بالأحداث بالترتيب ، والتأكد من أن الإشارات تصطف ، وعقد البيانات لفترة قصيرة.من رقائق الكمبيوتر إلى الأجهزة التي ترسل وتتلقى البيانات ، تعتبر D-Flip-Flops جزءًا رئيسيًا من كيفية عمل الإلكترونيات الحديثة.

D Flip-Flop لتخزين البيانات

الشكل 6. د فليب-فلاوب لتخزين البيانات

يوضح الشكل مجموعة من dlops dlip-flops متصلة بالتوازي ، كل تخزين جزء واحد من البيانات (D0 إلى D3).معا ، تشكل سجل 4 بت.تشترك جميع Flip-Flops في نفس إشارة الساعة (CLK) ، لذلك عندما يأتي نبض الساعة ، يتم تخزين جميع المدخلات في نفس الوقت وإرسالها إلى المخرجات (Q0 إلى Q3).يتم استخدام سجلات مثل هذه في ALUS لتخزين النتائج ، في أنظمة الإدخال/الإخراج لعقد البيانات أثناء التحويلات ، وفي وحدات التحكم لتتبع التعليمات.نظرًا لأن flip-flops يتم تشغيله على الحافة ، فإنهم يخزنون البيانات بدقة في كل حافة على مدار الساعة ، مما يساعد في توقيت دقيق.على الرغم من أن هذا النوع من التخزين مؤقت (يتم فقدان البيانات عند إيقاف الطاقة) ، إلا أنه سريع للغاية ، مما يجعله مفيدًا للمخازن المؤقتة والذاكرة قصيرة الأجل.

D Flip-Flops لنقل البيانات

الشكل 7. د flip-flops لنقل البيانات

يوضح الشكل d flip-flops المتصلة في سلسلة لتشكيل سجل Shift.تدخل البيانات بت واحدة في كل مرة من خلال إدخال البيانات التسلسلية وتنتقل من فليب واحد إلى آخر مع كل نبض نبض (إشارة الساعة).كل تقلبات تقلب وتمرر البيانات على طول خطوة بخطوة.وتسمى طريقة نقل البيانات هذه الاتصال التسلسلي.يتم استخدامه بشكل شائع في أنظمة مثل برامج التشغيل LED ، و UARTS (نقل المستقبِل غير المتزامن العالمي) ، ومولدات الإشارة.يمكن أيضًا جعل سجلات التحول مثل هذا أكثر تقدمًا مثل الأنواع ثنائية الاتجاه أو دائرية للمهام الخاصة مثل ترميز البيانات أو إضافة التأخير.نظرًا لأن البيانات تتحرك بطريقة يتم التحكم فيها ، فكل بت ، فإن هذا الإعداد فعال للأجهزة ذات النطاق الترددي المحدود أو المسافات الطويلة لإرسال إشارات.

تقسيم التردد

الشكل 8. تقسيم التردد

يوضح الشكل كيف يمكن لـ D flip-flop تقسيم تردد الإدخال.من خلال توصيل الإخراج Q 'مرة أخرى بإدخال D ، يقوم Flip-Flop بتبديل حالته في كل نبض على مدار الساعة.نتيجة لذلك ، يصبح تردد الإخراج نصف تردد الإدخال (F/2).غالبًا ما يتم استخدام هذه الطريقة لبناء مواسير التردد.من خلال تسلسل المزيد من الوجهات ، يمكنك إنشاء الفجوة-by-4 أو الانقسام إلى 8 أو أقسام أعلى ، ومفيدة في الساعات الرقمية ، ومولدات معدل الباود ، ودوائر أخذ العينات.هذا النهج بسيط وموثوق به ويستخدم الحد الأدنى من الأجهزة ، مما يجعله مثاليًا للتعامل مع التوقيت في الأنظمة الرقمية.

العدادات والوقت

D Flip-Flops هي لبنات بناء في العدادات الرقمية ودوائر التوقيت.عند ترتيبها في السلسلة ، يمكنهم تشكيل عدادات ثنائية أو عقد من الزمن تزيد إنتاجها مع كل نبض على مدار الساعة.تُستخدم هذه العدادات على نطاق واسع في الساعات الرقمية ، وعدادات التردد ، ودوائر المؤقت لقياس الوقت المنقضي ، أو أحداث العد ، أو توليد إشارات التحكم في توقيت.في تطبيقات المؤقت ، تساعد Flip-Flops في إنشاء تأخير دقيق عن طريق تقسيم تردد الساعة إلى فترات أطول يمكن التحكم فيها.نظرًا لطبيعتها الناجمة عن الحافة ، تضمن Dlip-Flops أن تحولات التهم والتوقيت تحدث في اللحظات المناسبة تمامًا ، مما يقلل من خطر الخلل أو أخطاء التوقيت في الدوائر الحساسة.

التواصل وتواصل الحافلات

في أنظمة الاتصالات الرقمية ، غالبًا ما يجب تخزين البيانات مؤقتًا أو متزامنة أو تحويلها بين المكونات التي تعمل بسرعات مختلفة.D Flip-Flops تلعب دورًا في هذه المهام.يتم استخدامها في سجلات التحول لتحويل البيانات بين التنسيقات التسلسلية والمتوازية في بروتوكولات مثل UART و SPI و I²C.بالإضافة إلى ذلك ، في تواصل الحافلات ، تساعد D flip-flops في وضع البيانات أثناء التحويلات ، مما يضمن أن يتم الاحتفاظ بالمعلومات لفترة طويلة بما يكفي لقراءتها أو كتابتها عبر خط ناقل.كما أنها تساعد في القضاء على عدم تطابق التوقيت بين أجزاء مختلفة من النظام ، مما يجعل الاتصال أكثر موثوقية ، وخاصة في الأنظمة التي لديها أجهزة متعددة خطوط البيانات.

أنظمة مضمنة

في التطبيقات المدمجة ، يتم استخدام dlip-flops لتخزين إشارات التحكم ، ومدخلات مستشعرات المزلاج ، وتتبع حالة النظم الفرعية الرقمية داخل موكئيات أو معالجات.تضمن قدرتهم على الحفاظ على البيانات حتى دورة الساعة التالية التشغيل المستقر ، حتى عند العمل مع الإشارات الصاخبة أو المتغيرة بسرعة.تساعد D Flip-Flops على تحقيق ذلك من خلال دعم إنشاء دوائر منطقية يمكن التنبؤ بها ، بما في ذلك آلات الحالة ، وحدات التحكم في التسلسل ، ودوائر التوقيت.كما أنها تستخدم في توليد نبضات ، وإشارات البوابات ، ومزامنة الأحداث.

مزايا d flip-flops

• إدخال بيانات واحد (د)

تتميز D Flip-Flops بإدخال بيانات واحد ، يُعرف ببساطة باسم "D" ، والذي يقوم بتبسيط تصميم الدوائر الرقمية.على عكس SR أو JK Flip-Flops التي تتطلب مدخلات متعددة ومنطق إضافي لإدارة حالات مختلفة ، تعمل D Flip-Flop بإدخال بيانات واحد فقط وإشارة ساعة.هذا يقلل من تعقيد التصميم ، ويقلل من الأخطاء في تعيين المنطق ، وتبسيط توجيه الإشارة في دوائر متكاملة.إنه مفيد في الأنظمة التي تحتاج إلى التحكم الدقيق للبيانات ، مثل السجلات ووحدات الذاكرة والتصاميم الحرجة.

• تجنب حالات غير صالحة

تتمثل إحدى القوة الرئيسية لـ D flip-flops في قدرتها على تجنب الحالات غير المحددة ، وهي مشكلة شائعة في SR Flip-Flops عند تنشيط كل من Set و Reset في وقت واحد.D Flip-Flops تتجنب ذلك باستخدام انقلاب منطقي بين إشارات التحكم الداخلية ، مما يضمن أن حالة تحكم واحدة فقط نشطة في وقت واحد.يعزز اختيار التصميم هذا الموثوقية والاتساق ، وهو مهم في بيئات السلامة الحرجة أو عالية الدقة.

• انخفاض استخدام الطاقة

تعتبر Dlip-Flops فعالة في الطاقة ، مما يجعلها مثالية للتطبيقات منخفضة الطاقة مثل الإلكترونيات المحمولة والأجهزة التي تعمل بالبطاريات.غالبًا ما يستخدمون التسجيل الشرطي (يتم تنشيطه فقط عند تغيير البيانات) والتحسينات الأخرى لتقليل التبديل غير الضروري ، مما يقلل من استهلاك الطاقة.مع وجود عدد أقل من البوابات الداخلية مقارنةً بوجه أكثر تعقيدًا مثل نوع JK ، فإنها أيضًا تقلل من فقدان الطاقة الثابتة والديناميكية.

• سلوك مستقر من الدولتين

كما هو الحال مع جميع Flip-Flops ، تعمل Dlip-Flops بطريقة ثنائية المستقرة ، يمكنها الاحتفاظ بواحدة من حالتين للإخراج (0 أو 1) حتى تطالب إشارة الساعة التالية بالتغيير.هذا يسمح لهم بالعمل كوحدات ذاكرة واحدة ، للمنطق المتسلسل ، وسجلات التحول ، والعدادات ، وآلات الدولة.تساعد قدرتهم على الاحتفاظ بالبيانات دون تحديث مستمر في الحفاظ على تدفق التحكم الموثوق في الدوائر الرقمية.

• هيكل داخلي بسيط

التكوين الداخلي لـ A D Flip-Flop واضح نسبيًا ، وغالبًا ما يتكون من مزلاج SR وعاكس لدقة التوقيت.يتناقض هذا مع JK أو T flip-flops ، والتي تتطلب ملاحظات أكثر تعقيدًا ومنطق التحكم.إن بساطة dlip-flops تجعلها أسهل في تنفيذها والتحقق منها وتصحيحها ، وسلوكها الذي يمكن التنبؤ به يجعلهم خيارًا أفضل في عمليات التصميم الآلية.

• عملية عالية السرعة

تم تصميم D Flip-Flops المصمم للأداء ، ويوفر تأخيرًا بسيطًا للانتشار بسبب الدوائر الداخلية الفعالة والتبديل المنطقي السريع.هذا يجعلها مثالية للتطبيقات عالية السرعة ، مثل معالجة الإشارات الرقمية وبروتوكولات الاتصال.طبيعتها التي تدور حولها الحافة تضمن التزامن دقيق مع إشارات الساعة.

• كفاءة المكون

D Flip-Flops موفرة للموارد ، وتتطلب عدد أقل من البوابات المنطقية والترانزستورات من الأنواع الأخرى.يترجم هذا التصميم المدمج إلى مساحة رقاقة أصغر ، وتكاليف مخفضة ، وإمكانية زيادة كثافة التكامل في ICS.يؤدي استخدامها الحد الأدنى للمكونات أيضًا إلى انخفاض تأثيرات الطفيليات ، مما يعزز كل من السرعة وكفاءة الطاقة للأنظمة الرقمية على نطاق واسع وعالي الأداء.

عيوب d flip-flops

• عدم وجود آليات التغذية المرتدة الداخلية

تم تصميم Dlip-flops لتخزين جزء واحد من البيانات يعتمد على إشارات الإدخال والساعة ، ويفتقر إلى أي قدرة على التغذية المرتدة.هذا يعني أنهم لا يستطيعون ضبط إخراجهم بناءً على الحالات السابقة أو المنطق الداخلي.في التطبيقات التي تكون فيها التغذية المرتدة مثل أنظمة التحكم في المحرك ، أو حلقات PID ، أو التصفية التكيفية ، يجب تقديم الدوائر الخارجية لمحاكاة التعليقات.على سبيل المثال ، يضيف توصيل الإخراج مرة أخرى إلى البوابات المنطقية التعقيد ، ويزيد من عدد المكونات ، ويعقد تحليل التوقيت ، مما قد يقلل من استجابة النظام واستقراره.

• لا توجد وظيفة تبادل أصلية

لا تقوم Dlip-flops بتبديل إخراجها بطبيعتها مع كل نبضة على مدار الساعة ؛بدلاً من ذلك ، فإنها تعكس المدخلات على حافة تشغيل الساعة.هذا يجعلها غير مناسبة للاستخدام المباشر في العدادات أو مقسمات التردد ، حيث يلزم تبديل السلوك.يمكن أن تعمل محاكاة تقلب t من خلال توصيل الإخراج المقلوب بإدخال البيانات ، لكن هذا يضيف أسلاكًا إضافية ، ويزيد من التعرض لإشارة مشكلات النزاهة ، ويتطلب توقيتًا دقيقًا لتجنب ظروف السباق خاصة في الدوائر عالية السرعة.

• تأخير الانتشار

مثل كل التقلبات ، فإن أنواع D تقدم تأخير الانتشار ، والوقت بين حافة الساعة وتغيير الإخراج المقابل.بينما في كثير من الأحيان في نطاق النانو ثانية ، يمكن أن يتراكم هذا التأخير في أنظمة عالية السرعة أو أنابيب بعمق ، مما قد يتسبب في انتهاكات توقيت أو مواطن الخلل أو الانحراف.يتم استخدام تحليل التوقيت الدقيق ، غالبًا مع أدوات المحاكاة ومخططات التوقيت التفصيلية ، في مثل هذه التصميمات لضمان الاستقرار والصحة.

• الإعداد وحساسية الوقت

تتطلب Dlip-Flops أن تظل إدخال البيانات مستقرة لنافذة موجزة قبل وبعد حافة الساعة ، والمعروفة باسم الإعداد ووقت عقد.إذا تم انتهاك هذا المطلب كما هو الحال عند حدوث انتقالات البيانات بالقرب من الساعة ، فقد تنتج المخرجات الخاطئة أو غير المتوقعة.في التصميمات عالية السرعة أو المعقدة ، قد يكون تلبية قيود التوقيت هذه أمرًا صعبًا ، وغالبًا ما يتطلب استخدام المخازن المؤقتة أو موازنة المسار الدقيق ، وزيادة تعقيد التصميم وتقليل هوامش التوقيت.

• خطر الانفصال

تحدث القابلية النقيلية عندما يتلقى Flip-Flop انتقالات الإدخال بالقرب من حافة الساعة ، وغالبًا ما تكون من مصادر غير متزامنة ، مما تسبب في دخولها إلى حالة غير مستقرة قد تستغرق بعض الوقت لحلها.خلال هذه الفترة ، قد يتأرجح الإخراج أو ينتج عنه مستويات منطقية غير محددة.هذا أمر خطير في الأنظمة التي يكون فيها السلوك الحتمي مهمًا ، كما هو الحال عند عبور مجالات الساعة.للتخفيف من ذلك ، استخدم دوائر Synchronizer أو Flip-Flops المصممة للتعامل مع قابلية النقيض بأمان أكثر.

• وظائف مدمجة محدودة

على الرغم من أن Dlip-Flops بسيطة ومستخدمة على نطاق واسع ، توفر فقط وظائف إغلاق البيانات الأساسية.على النقيض من ذلك ، تدعم JK أو SR Flip-Flops عمليات أكثر تعقيدًا مثل التبديل أو ظروف التعيين/إعادة تعيين متزامنة دون منطق إضافي.غالبًا ما تفتقر Dlip-flops إلى مسبق غير متزامن ومدخلات واضحة ما لم يتم تصميمها على وجه التحديد ، مما يحد من مرونتها في سيناريوهات التحكم معينة.بالنسبة للتطبيقات التي تتطلب سلوكًا أكثر دقة خلال دورة ساعة واحدة ، يجب أن تكمل بوابات إضافية ومنطق Dlip-Flops ، مما يزيد من تعقيد الدائرة وجهود التصميم.

خاتمة

تعتبر Dlip-Flops مفيدة للغاية في الإلكترونيات الرقمية لأنها يمكنها تخزين البيانات والحفاظ عليها مستقرة باستخدام إشارات الساعة.إنها بسيطة للاستخدام ، وتجنب أخطاء مثل الحالات غير الصالحة ، وتعمل بشكل جيد في أنظمة سريعة ومنخفضة الطاقة.يمكنك استخدامها في السجلات والمزالج والعدادات ودوائر نقل البيانات.كما أنها مفيدة في أنظمة مثل متحكمها وأجهزة الاتصال.لكن لديهم بعض الجوانب السلبية ، مثل التأخير في وقت الاستجابة ، والحاجة إلى توقيت دقيق ، وعدم وجود ملاحظات مدمجة أو وظائف تبديل.يساعد معرفة نقاط القوة والضعف في تصميم أنظمة رقمية أفضل.

معلومات عنا

ALLELCO LIMITED

قراءة المزيد

تحقيق سريع

الرجاء إرسال استفسار ، وسوف نرد على الفور.

أسئلة مكررة [FAQ]

1. ما هو الشكل القياسي لـ D Flip-Flop؟

يحتوي D Flip-Flop على ثلاثة أجزاء رئيسية: إدخال بيانات (D) ، ومدخل الساعة (CLK) ، ومخرجين (Q و Q ′).إنه يعمل عن طريق نسخ القيمة من إدخال D إلى إخراج Q فقط عندما تتغير إشارة الساعة ، وعادةً ما تكون على الحافة الصاعدة (من منخفضة إلى عالية).بعد تلك اللحظة ، يبقى الإخراج كما هو حتى لو تغير المدخلات.يجعل هذا الإعداد D flip-flop مفيدًا لتخزين جزء واحد من المعلومات في وقت محدد.إن Flip-Flop القياسي بسيط وموثوق به ، مما يجعله شائعًا في دوائر الذاكرة والأنظمة الرقمية.

2. ما هي معادلة d flip-flops؟

القاعدة الرئيسية لـ A D Flip-Flop بسيطة: يصبح الإخراج Q مساويًا للإدخال D عند تتغير إشارة الساعة.يمكن كتابة هذا على أنه Q (التالي) = D. يعني أي قيمة عند إدخال D في الوقت الحالي يتم تمرير حافة الساعة إلى إخراج Q.يتجاهل Flip-Flop جميع التغييرات الأخرى حتى حافة الساعة التالية.هذا يجعل D flip-flops سهلة الاستخدام وفهم في التصميمات الرقمية.

3. ما هو تردد الإخراج من D flip-flop؟

إذا قمت بتوصيل إدخال D بعكس إخراج Q (Q ′) ، فسيقوم Dlip-Flop بتبديل حالته في كل مرة يتم فيها تحديد إشارة إشارة الساعة.هذا يجعل تردد التردد الناتج من تردد الساعة.لذلك ، إذا كانت الساعة 8 ميغاهيرتز ، يصبح الناتج 4 ميغاهيرتز.غالبًا ما يتم استخدام هذا الإعداد في الدوائر لتقسيم التردد ، كما هو الحال في أجهزة ضبط الوقت أو العدادات.

4. ما هو الفرق بين D و T Flip-Flops؟

يقوم D Flip-Flop بنسخ الإدخال (D) إلى الإخراج (Q) عندما تتغير الساعة.يتم استخدامه لتخزين البيانات.يعمل T flip-flop بشكل مختلف ، فإنه يتغير أو "تبديل" ناتجه في كل مرة يتم فيها وضع علامة على مدار الساعة ، ولكن فقط إذا كان إدخال T مرتفعًا.إذا كان T منخفضًا ، فلن يحدث شيء.يتم استخدام Dlip-flops للاحتفاظ بالبيانات ، في حين يتم استخدام T flip-flops لبناء عدادات وتقسيم إشارات الساعة.يتصرفون بشكل مختلف على الرغم من أن كلاهما يتم تشغيله على مدار الساعة.

5. ما هو الفرق بين AT و D Flip-Flop؟

لا يوجد قلب قياسي يسمى "في Flip-Flop".قد يكون هذا خطأً أو خطأ مطبعي ، وربما كان من المفترض أن يقول "t flip-flop".إذا كان هذا هو الحال ، فإن الفرق بسيط: A D Flip-Flop يخزن القيمة عند إدخال D عند وضع علامة على مدار الساعة ، في حين أن T flip-flop يتبديل إخراجها (يتحول بين 0 و 1) إذا كان الإدخال T مرتفعًا.لذلك ، فإن dlip-flops مخصصة لتخزين البيانات ، و t flip-flops هي لتبديل الحالات.إذا كان "AT" يعني شيئًا آخر ، فيجب تفسيره بشكل أكثر وضوحًا.

نظرة عامة كاملة على XC4044XL-3BG432C FPGA

على 02/06/2025

دليلك إلى mpc8247czqtiea من freescale

على 30/05/2025

الوظائف الشعبية

-

أجهزة الكمبيوتر المعقدة لتعليمات التعليمات: كيف غيرت الحوسبة؟

على 18/04/8000 147749

-

usb-c pinout والميزات

على 18/04/2000 111908

-

باستخدام بدائل المحاكاة الموحدة Xilinx: دليل شامل لتصميم ومحاكاة FPGA

على 18/04/1600 111349

-

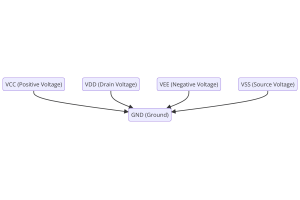

جهد مصدر الطاقة في الإلكترونيات: معنى VCC، VDD، VEE، VSS، وGND

على 18/04/0400 83714

-

دليل موصل RJ45: pinout ، الأسلاك ، أنواع الكابلات ، والاستخدامات

على 01/01/1970 79502

-

الدليل النهائي لرموز الألوان السلكية في الأنظمة الكهربائية الحديثة

الطريقة التي تستخدمها أنظمةنا الكهربائية بالألوان ليست فقط للمظهر.يشير كل لون سلك الآن إلى وظيفة محددة ، مما يسهل تحديد المكونات الكهربائية والتعامل معها بشكل صحيح أثناء التثبيت والصيانة.هذا لا يسر...على 01/01/1970 66869

-

الجودة (س) العامل: المعادلات والتطبيقات

يعد عامل الجودة ، أو "Q" مهمًا عند التحقق من مدى عمل المحاثات والراتين في الأنظمة الإلكترونية التي تستخدم ترددات الراديو (RF).يقيس "Q" مدى تقليل الدائرة إلى تقليل فقدان الطاقة وتؤثر على نطاق التردد...على 01/01/1970 63004

-

دليل Purge Valve: الوظيفة والأعراض والاختبار والاستبدال لأداء المحرك الأمثل

يعد Purge Valve جزءًا رئيسيًا من نظام السيارة الذي يساعد في الحفاظ على نظافة الهواء من خلال إدارة أبخرة الوقود قبل أن يتمكنوا من الهروب إلى الجو.هذا لا يساعد البيئة فقط عن طريق تقليل التلوث ولكن أي...على 01/01/1970 62947

-

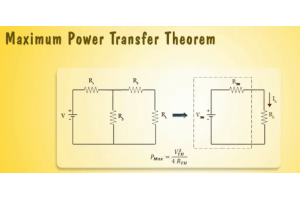

تحقيق ذروة أداء مع أقصى نظرية نقل الطاقة

تشرح نظرية نقل الطاقة القصوى كيف تتدفق الطاقة من مصدر ، مثل البطارية أو المولد ، إلى الحمل المتصل.يوضح الحالة الدقيقة التي يتلقى فيها الحمل أكثر الطاقة.تغطي هذه المقالة ما تعنيه النظرية ، وكيف تعمل...على 01/01/1970 54077

-

مواصفات البطارية A23 وتوافقها

بطارية A23 عبارة عن بطارية صغيرة على شكل أسطوانة مع جهد عالي.يُطلق عليه أيضًا 23a أو 23ae أو Mn21 ، ويتم تشغيله بسرعة 12 فولت وأعلى بكثير من بطاريات AA أو AAA.تصميمه الخاص يجعلها مثالية لل...على 01/01/1970 52089