EP2S60F672C4 FPGA: الميزات والتطبيقات والبرمجة ودليل ورقة البيانات

في هذا الدليل ، ستحصل على نظرة عامة واضحة على EP2S60F672C4 ، وهو FPGA قوي من عائلة Intel’s Stratix II.ستتعرف على ميزاتها الرئيسية ، والهندسة المعمارية ، وهيكل الكتلة ، والمواصفات الفنية لفهم كيفية ملاءمة التصميمات الرقمية المتقدمة.كما أنه يمر بك من خلال خطوات البرمجة والتطبيقات والمزايا والعيوب حتى تتمكن من معرفة أين يمكن استخدام هذا الجهاز بالضبط.كتالوج

ما هو EP2S60F672C4؟

ال EP2S60F672C4 هو FPGA عالي الكثافة من Intel (المعروف سابقًا باسم Altera) ، ينتمي إلى عائلة Stratix II.تم تصميمه على عملية SRAM بنحو 90 نانومتر ، 1.2 فولت ، وهي توفر قدرة منطقية كبيرة ضمن حزمة FBGA 672 كرة ، مما يجعلها مثالية للأنظمة الرقمية المعقدة.كجزء من سلسلة EP2S ، يجلس جهاز "60" في نطاق من منتصف إلى متوسطة في تشكيلة Stratix II ، مما يوفر توازنًا قويًا في كثافة المنطق ، والذاكرة المدمجة ، وموارد I/O.تشتهر هذه FPGA بعمارةها القوية وموثوقيتها ، لا تزال خيارًا موثوقًا به في العديد من التصميمات المتقدمة.

هل تبحث عن EP2S60F672C4؟اتصل بنا للتحقق من الأسهم الحالية ، وتهمة المهلة ، والتسعير.

EP2S60F672C4 CAD نماذج

EP2S60F672C4 رمز

EP2S60F672C4 بصمة

EP2S60F672C4 3D نموذج

EP2S60F672C4 ميزات

• 90 نانومتر المتقدمة ، 1.2 فولت CMOS عملية

تم تصنيع EP2S60F672C4 على عملية CMOs النحاسية التي تبلغ تكلفتها 90 نانومتر والتي يتم تشغيلها عند جهد أساسي 1.2 فولت.تتيح هذه التكنولوجيا السرعة العالية ، وتقليل استهلاك الطاقة ، وكثافة منطقية أكبر مقارنة بأجيال FPGA الأقدم.

• بنية وحدة المنطق التكيفي (ALM)

يستخدم الجهاز الصقة كبناء للمنطق بدلاً من العناصر المنطقية التقليدية.تعمل هذه البنية على تحسين استخدام الموارد ، مما يسمح بتنفيذ وظائف منطقية أكثر تعقيدًا بكفاءة داخل نفس منطقة السيليكون.

• كثافة المنطق العالية

مع ما يقرب من 60،440 عنصر منطقي (24،176 صدق) ، يدعم FPGA التصاميم الرقمية الكبيرة والمتطورة.هذه السعة العالية تجعلها مناسبة للتطبيقات مثل معالجة الإشارات والاتصالات وأنظمة التحكم المدمجة.

• Trimatrix ™ الذاكرة على الرقاقة

يدمج EP2S60F672C4 ثلاثة أنواع من كتل RAM ، (M512 ، M4K ، و M-RAM) لتوفير ما مجموعه حوالي 2.4 ميجابت من الذاكرة المدمجة.يسمح هذا المزيج بتنفيذ FIFOs الصغيرة ، المخازن المؤقتة المتوسطة ، وذكريات المنفذ المزدوجة الكبيرة بكفاءة.

• كتل DSP مخصصة

يتضمن الجهاز 36 كتل DSP مخصصة مصممة للعمليات الحسابية مثل الضربات والتراكم وتصفية التنوب.هذه الكتل تعزز الأداء في المهام كثيفة الحساب مع توفير الموارد المنطقية العامة.

• I/O عالية السرعة وسلامة الإشارة

وهو يدعم العديد من معايير الإدخال/الإخراج التفاضلية أحادية الطابق والتفاضلي جنبًا إلى جنب مع دوائر محاذاة المرحلة الديناميكية (DPA).تتيح هذه الميزات نقل البيانات المستقرة وعالية السرعة إلى 1 جيجابت في الثانية ، مما يضمن اتصالًا موثوقًا به مع مكونات خارجية.

• دعم واجهة الذاكرة الخارجية الغنية

FPGA متوافق مع DDR ، DDR2 ، QDR II ، RLDRAM II ، ومعايير الذاكرة الأخرى.يؤدي دعم الواجهة المدمج إلى تبسيط تصميم اللوحة ويحقق إنتاجية عالية للبيانات للتطبيقات المكثفة للذاكرة.

• إدارة الساعة المرنة

تسمح ما يصل إلى 12 PLLs على الرقاقة بضرب الساعة ، والتقسيم ، وتحويل الطور ، والتبديل الخالي من الخلل.يمكنك ضبط المجالات على مدار الساعة وتقليل الارتعاش ، ودعم ترددات الساعة الداخلية التي تصل إلى 500 إلى 550 ميجا هرتز.

• تشفير Bitstream وإعادة التكوين

يدعم EP2S60F672C4 تشفير BitStream المستند إلى AES لتأمين الملكية الفكرية.كما يوفر إمكانية إعادة التكوين عن بُعد ، مما يتيح التحديثات في الميدان دون استبدال الجهاز.

مخطط كتلة Stratix II

يوضح مخطط كتلة Stratix II ، كما هو موضح في EP2S60F672C4 ، الترتيب الداخلي للمنطق والذاكرة وموارد DSP التي تشكل جوهر FPGA.يتم ترتيب كتل مجموعة المنطق (LABS) في شبكة منتظمة ، وتحيط بها RAM المدمج وأعمدة DSP ، والتي توفر إمكانات تخزين سريعة الحساب وعلى الرقاقة.عناصر الإدخال/الإخراج المحيطية وشبكات الساعة تأطير هذا الهيكل ، مما يتيح نقل البيانات الفعال والتحكم في التوقيت بين FPGA والأجهزة الخارجية.هذا الرسم التخطيطي مهم لأنه يساعد في فهم كيفية تنظيم الكتل الوظيفية المختلفة جسديًا ، مما يسمح لها بتحسين الموضع والتوجيه وأداء النظام العام.

مخطط بنوك Stratix II I/O

يوضح مخطط البنوك في Stratix II I/O كيف يتم تجميع دبابيس الإدخال/الإخراج في EP2S60F672C4 وما تدعم كل مجموعة.تم تصميم كل بنك I/O للتعامل مع مستويات جهد محددة وأنواع الإشارات ووظائف مثل LVTTL أو SSTL أو LVDs أو معايير إدخال الساعة.يوضح التصميم كيف يتم تحسين البنوك المختلفة (على سبيل المثال ، 1 ، 2 ، 5 ، 6 مقابل 3 ، 4 ، 7 ، 8 ، إلخ) إما لإشارة I/O للأغراض العامة أو الإشارة التفاضلية عالية السرعة ، بما في ذلك دعم مدخلات ساعة LVDS/LVPECL على الحواف.يعد فهم هذا الهيكل أمرًا مهمًا عند تعيين دبابيس ، لأن الاختيار المصرفي المناسب يضمن التوافق الكهربائي ، ويؤدي إلى تبسيط توجيه اللوحة ، ويزيد من أداء FPGA في التصميمات عالية السرعة.

EP2S60F672C4 مواصفات

|

يكتب |

المعلمة |

|

الشركة المصنعة |

Altera/Intel |

|

مسلسل |

Stratix® II |

|

التغليف |

صينية |

|

حالة الجزء |

عفا عليها الزمن |

|

عدد المختبرات/CLBs |

3022 |

|

عدد العناصر/الخلايا المنطقية |

60،440 |

|

مجموع البتات الكبش |

2،544،192 |

|

عدد i/o |

492 |

|

الجهد - العرض |

1.15 V ~ 1.25 V |

|

نوع التثبيت |

جبل السطح |

|

درجة حرارة التشغيل |

0 درجة مئوية ~ 85 درجة مئوية (TJ) |

|

حزمة / حالة |

672-BBGA |

|

حزمة جهاز المورد |

672-FBGA (27 × 27) |

|

رقم المنتج الأساسي |

EP2S60 |

تطبيقات EP2S60F672C4

1. معالجة الإشارات الرقمية (DSP) والتصفية

EP2S60F672C4 مناسب تمامًا لتنفيذ وظائف DSP عالية الأداء مثل مرشحات FIR و IIR ومعالجة FFT والعمليات الحسابية المعقدة.تعامل كتل DSP المخصصة الخاصة به بالتكاثر وتراكمها بكفاءة ، مما يحرر الموارد المنطقية العامة للمهام الأخرى.تتيح ذاكرة TrimTrix ™ على الرقاقة التخزين المؤقت للبيانات وخزان الأنابيب ، وهو أمر رائع للمعالجة في الوقت الفعلي بمعدلات عينة عالية.هذا يجعل الجهاز مثاليًا لتطبيقات إشارة الصوت والفيديو والرادار المتقدمة.

2. الاتصالات عالية السرعة والشبكات

تدعم واجهات I/O عالية السرعة من FPGA ودوائر محاذاة المرحلة الديناميكية (DPA) ناقل حركة موثوق على مستوى جيجابت.يمكنه تنفيذ بروتوكولات الاتصال ووظائف الطبقة المادية لأنظمة مثل أجهزة التوجيه والمفاتيح وترابط الطائرة الخلفية.بفضل قدرتها المنطقية الكبيرة و PLLs المرنة ، يمكنها إدارة تحويلات التوقيت والبروتوكول المعقدة بين واجهات متعددة عالية السرعة.هذه القدرات تجعلها مناسبة قوية للبنية التحتية للاتصالات ومعدات الشبكات عالية النطاق الترددي.

3. وحدات التحكم في الذاكرة وأنظمة معالجة البيانات

يدعم EP2S60F672C4 العديد من واجهات الذاكرة الخارجية بما في ذلك DDR ، DDR2 ، RLDRAM II ، و QDR II ، مما يجعلها مثالية لتصميم وحدات التحكم في الذاكرة عالية النطاق.يمكنه التعامل مع التخزين المؤقت للبيانات ، وتوليد العناوين ، والتحكيم بسرعات عالية مع الحد الأدنى من الكمون.يتيح الجمع بين شبكات الساعة السريعة وكتل ذاكرة الوصول العشوائي المدمجة إدارة فعالة لتيارات البيانات الكبيرة.هذا يجعل FPGA مناسبًا لمعالجة الصور ، وتدفق الفيديو ، ومنصات الحساب العلمي التي تعتمد على إنتاجية البيانات الثقيلة.

4. المنطق المخصص والتسارع المدمج

مع أكثر من 60،000 عنصر منطقي وإدارة الساعة الغنية ، يمكن لـ FPGA استضافة مسرعات الأجهزة المخصصة لخوارزميات محددة.غالبًا ما يستخدمه المصممون لتفريغ المهام المكثفة من الناحية الحسابية من وحدات المعالجة المركزية ، مثل التشفير ، أو تحليل البروتوكول ، أو حلقات التحكم في الوقت الفعلي.يمكنه أيضًا دمج كتل وظيفية متعددة ، مما يجعلها مناسبة للتصاميم المعقدة التي تشبه SOC.هذه المرونة تجعلها ذات قيمة في التطبيقات مثل الأتمتة الصناعية وأنظمة الأمان ووحدات التحكم في الطيران.

5. منصات النماذج الأولية والتنمية التعليمية

تم العثور على جهاز EP2S60 عادة على مجموعات تطوير FPGA المستخدمة في النماذج الأولية والاختبار والبحث الأكاديمي.يتيح توازن السعة المنطقية ، وعدد الإدخال/الإخراج ، وقدرات DSP المهندسين والطلاب بتنفيذ الأنظمة الكاملة والتحقق منها على شريحة واحدة.وهو يدعم التكرار السريع للتصميمات الرقمية ، مما يتيح التحقق من الأجهزة قبل الالتزام بتطوير ASIC.تستخدمها العديد من الجامعات ومختبرات البحث والتطوير لتدريس مفاهيم التصميم الرقمي المتقدم ومعالجة الإشارات.

EP2S60F672C4 أجزاء مماثلة

|

مواصفة |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672I4

|

EP2S60F672I3N |

|

الأسرة / السلسلة |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

|

العناصر المنطقية (LE) |

60،440 |

60،440 |

60،440 |

60،440 |

60،440 |

60،440 |

|

الصدقات |

24176 |

24176 |

24176 |

24176 |

24176 |

24176 |

|

طَرد |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

درجة السرعة |

C4 (STD) |

C3 (أسرع) |

C5 (أسرع) |

C5 (أسرع) |

i4 (STD) |

i3 (أسرع) |

|

درجة الحرارة |

تجاري (0 ~ 70 درجة مئوية) |

تجاري |

تجاري |

تجاري |

الصناعي (-40 ~ 100 درجة مئوية) |

الصناعي (-40 ~ 100 درجة مئوية) |

|

دبابيس I/O. |

492 |

492 |

492 |

492 |

492 |

492 |

|

الذاكرة على الرقاقة |

2.4 ميجابت |

2.4 ميجابت |

2.4 ميجابت |

2.4 ميجابت |

2.4 ميجابت |

2.4 ميجابت |

|

الجهد الأساسي |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

|

اختلاف رئيسي |

السرعة التجارية الأساسية |

C3 SPEED BIN ، خالية من الرصاص "N" |

عالي السرعة سلة |

سلة عالية السرعة ، "N" البديل |

درجة الحرارة الصناعية ، نفس الكثافة |

الصناعي ، سرعة أسرع ، خالية من الرصاص |

EP2S60F672C4 خطوات البرمجة

قبل أن تتمكن من استخدام EP2S60F672C4 FPGA في التصميم الخاص بك ، تحتاج إلى تكوينه بشكل صحيح مع BitStream المترجمة.تتضمن هذه العملية إعداد ملف البرمجة ، وإعداد واجهة الأجهزة ، وضمان تحميل التكوين بشكل صحيح على الطاقة.

الخطوة 1: إنشاء وتجميع التصميم الخاص بك

تبدأ بتطوير تصميم المنطق الخاص بك باستخدام برنامج Intel Quartus II.بعد الانتهاء من التصميم ، تقوم بتجميعه لإنشاء ملف البرمجة (.sof أو .pof) خصيصًا لجهاز EP2S60F672C4.تقوم عملية التجميع بالتحقق من التوقيت ، وتعيينات الدبوس ، واستخدام الموارد لضمان أن التصميم الخاص بك يناسب بنية FPGA.بمجرد التجميع ، يكون Bitstream جاهزًا لتكوين الجهاز.

الخطوة 2: إعداد أجهزة البرمجة

بعد ذلك ، تقوم بإعداد واجهة البرمجة المادية بين جهاز الكمبيوتر الخاص بك ولوحة FPGA.عادةً ما يتضمن ذلك توصيل كابل JTAG USB-Blaster أو كابل JTAG المتوافق بمنفذ JTAG الخاص بالجهاز.يجب عليك التحقق من أن Quartus II يتعرف على المبرمج وأنه تم اكتشاف الجهاز المستهدف بشكل صحيح.تضمن هذه الخطوة التواصل المستقر قبل بدء عملية التكوين.

الخطوة 3: تحميل ملف البرمجة في الجهاز

باستخدام أداة مبرمج Quartus II ، يمكنك إضافة ملف .sof أو .pof المترجمة وتحديد EP2S60F672C4 من قائمة الأجهزة المكتشفة.يمكنك بعد ذلك بدء تسلسل البرمجة ، حيث يتم نقل BitStream خلالها إلى خلايا تكوين SRAM الخاصة بـ FPGA.يجب عليك مراقبة شريط التقدم ورسائل الحالة لتأكيد التكوين الناجح.بمجرد الانتهاء ، يبدأ FPGA في تنفيذ المنطق المبرمج على الفور.

الخطوة 4: تحقق من التكوين والتشغيل

بعد البرمجة ، يمكنك التحقق من أن الجهاز يعمل على النحو المقصود.يوفر Quartus II خيار التحقق للتحقق من إشارات التكوين وإشارات الحالة ، مما يضمن تحميل التصميم بشكل صحيح.يمكنك أيضًا اختبار وظائف الإدخال/الإخراج أو تشغيل محاكاة وظيفية لتأكيد سلوك النظام.تضمن هذه الخطوة الأخيرة أن التصميم الخاص بك يعمل بشكل كامل ومستقر على الأجهزة.

EP2S60F672C4 مزايا وعيوب

المزايا

• كثافة منطقية عالية للتصميمات المعقدة

• نسبة أداء جيدة إلى تكلفة

• الهجرة السهلة داخل نفس العائلة

• أدوات التنمية المستقرة والناضجة

• موثوقية مثبتة في الاستخدام الصناعي

عيوب

• عفا عليها الزمن وأصعب للمصدر

• استهلاك الطاقة الأعلى من أحدث FPGAs

• لا توجد أجهزة استقبال حديثة عالية السرعة

• إغلاق توقيت أكثر صعوبة عند الاستخدام العالي

• قابلية التوسع المحدودة للبروتوكولات المستقبلية

EP2S60F672C4 أبعاد التغليف

|

يكتب |

المعلمة |

|

نوع الحزمة |

672-FBGA (Fineline BGA) |

|

حجم الجسم (L × W) |

27.00 مم × 27.00 مم |

|

إجمالي ارتفاع الحزمة (أ) |

الحد الأقصى 3.50 مم |

|

ارتفاع المواجهة (A1) |

دقيقة 0.30 مم |

|

سمك الركيزة (A2) |

الحد الأقصى 3.00 مم |

|

قطر الكرة (ب) |

0.50 مم - 0.70 ملم |

|

كرة الكرة (هـ) |

1.00 مم |

|

عدد الكرات |

672 |

|

نمط التثبيت |

جبل السطح |

|

وصف الحزمة |

FBGA ، 27 × 27 مم شبكة |

EP2S60F672C4 الشركة المصنعة

يتم تصنيع EP2S60F672C4 FPGA بواسطة شركة Altera، رائد رائد في الأجهزة المنطقية القابلة للبرمجة.في عام 2015 ، تم الحصول على Altera بواسطة إنتل، ويندرج المنتج الآن في إطار مجموعة Intel القابلة للبرمجة (PSG) ، والتي تستمر في دعم وتزويد عائلات FPGA المعمول بها.تحافظ Intel على خط Stratix II كجزء من محفظة منتجاتها القديمة ، مما يضمن الوثائق ودعم الأدوات وتوافرها على المدى الطويل للتطبيقات الصناعية والاتصالات.

خاتمة

يجمع EP2S60F672C4 بين كثافة المنطق العالية ، بنية الذاكرة المرنة ، وميزات I/O قوية لدعم الأنظمة الرقمية المعقدة.تتيح تصميمها المستند إلى ALM ، وذاكرة Trimatrix ™ ، وكتل DSP ، وميزات إدارة الساعة ، تنفيذًا فعالًا للتطبيقات الصعبة.على الرغم من أنه يوفر موثوقية مثبتة ودعم تنمية ناضج ، فإنه يواجه قيودًا مثل التقادم ونقص أجهزة الإرسال والاستقبال الحديثة مقارنة بأجيال FPGA الأحدث.بشكل عام ، يجعل أداءها المتوازن وتنوعه خيارًا قويًا لمعالجة الإشارات والاتصالات ومعالجة البيانات وتطبيقات النماذج الأولية.

ورقة البيانات pdf

EP2S60F672C4 أوراق البيانات:

معلومات عنا

ALLELCO LIMITED

قراءة المزيد

تحقيق سريع

الرجاء إرسال استفسار ، وسوف نرد على الفور.

أسئلة مكررة [FAQ]

1. هل يمكن أن يعمل EP2S60F672C4 مع واجهات ذاكرة DDR الحديثة؟

نعم ، يدعم واجهات DDR و DDR2 و QDR II و RLDRAM II ، والتي تغطي العديد من معايير الذاكرة الخارجية الشائعة.هذا يجعلها مناسبة لتطبيقات معالجة البيانات عالية النطاق الترددي.

2. هل يتطلب EP2S60F672C4 معالجة أو تخزين خاصة؟

نعم ، مثل المكونات الأخرى المعبأة في BGA ، يجب تخزينها في عبوة تسيطر عليها الرطوبة والتعامل معها مع حماية ESD.بعد ممارسات التخزين المناسبة تساعد على الحفاظ على قابلية اللحام وموثوقية الجهاز أثناء التجميع.

3. كيف يمكنك تقليل استهلاك الطاقة في تصميمات EP2S60F672C4؟

يمكنك تحسين استخدام المنطق ، والساعات غير المستخدمة بوابة ، وخفض الفولتية I/O حيثما أمكن ، والاستفادة من خيارات توليف الطاقة في Quartus II لتقليل السحب الإجمالي للطاقة.

4. ما هي أدوات البرمجة المطلوبة لـ EP2S60F672C4؟

ستحتاج إلى برنامج Intel Quartus II للتصميم والتجميع والبرمجة ، إلى جانب USB-Blaster أو كابل JTAG متوافق لتكوين الجهاز.

5. هل يدعم EP2S60F672C4 التحديثات في الميدان أو إعادة التكوين عن بُعد؟

نعم ، إنه يدعم تشفير Bitstream المستند إلى AES وإعادة تكوينه عن بُعد ، مما يتيح لك تحديث نظامك بشكل آمن دون استبدال FPGA جسديًا.

كل شيء عن LFXP6C-3FN256C شعرية أشباه الموصلات

على 06/10/2025

XC2C256-7TQ144C CPLD: Pinout ، الميزات ، دليل برمجة ورقة البيانات

على 03/10/2025

الوظائف الشعبية

-

أجهزة الكمبيوتر المعقدة لتعليمات التعليمات: كيف غيرت الحوسبة؟

على 19/04/8000 147782

-

usb-c pinout والميزات

على 19/04/2000 112062

-

باستخدام بدائل المحاكاة الموحدة Xilinx: دليل شامل لتصميم ومحاكاة FPGA

على 19/04/1600 111352

-

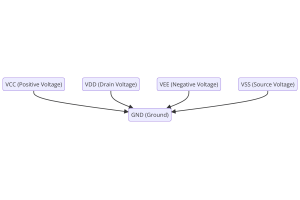

جهد مصدر الطاقة في الإلكترونيات: معنى VCC، VDD، VEE، VSS، وGND

على 19/04/0400 83819

-

دليل موصل RJ45: pinout ، الأسلاك ، أنواع الكابلات ، والاستخدامات

على 01/01/1970 79639

-

الدليل النهائي لرموز الألوان السلكية في الأنظمة الكهربائية الحديثة

الطريقة التي تستخدمها أنظمةنا الكهربائية بالألوان ليست فقط للمظهر.يشير كل لون سلك الآن إلى وظيفة محددة ، مما يسهل تحديد المكونات الكهربائية والتعامل معها بشكل صحيح أثناء التثبيت والصيانة.هذا لا يسر...على 01/01/1970 66999

-

دليل Purge Valve: الوظيفة والأعراض والاختبار والاستبدال لأداء المحرك الأمثل

يعد Purge Valve جزءًا رئيسيًا من نظام السيارة الذي يساعد في الحفاظ على نظافة الهواء من خلال إدارة أبخرة الوقود قبل أن يتمكنوا من الهروب إلى الجو.هذا لا يساعد البيئة فقط عن طريق تقليل التلوث ولكن أي...على 01/01/1970 63124

-

الجودة (س) العامل: المعادلات والتطبيقات

يعد عامل الجودة ، أو "Q" مهمًا عند التحقق من مدى عمل المحاثات والراتين في الأنظمة الإلكترونية التي تستخدم ترددات الراديو (RF).يقيس "Q" مدى تقليل الدائرة إلى تقليل فقدان الطاقة وتؤثر على نطاق التردد...على 01/01/1970 63062

-

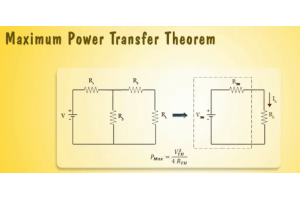

تحقيق ذروة أداء مع أقصى نظرية نقل الطاقة

تشرح نظرية نقل الطاقة القصوى كيف تتدفق الطاقة من مصدر ، مثل البطارية أو المولد ، إلى الحمل المتصل.يوضح الحالة الدقيقة التي يتلقى فيها الحمل أكثر الطاقة.تغطي هذه المقالة ما تعنيه النظرية ، وكيف تعمل...على 01/01/1970 54097

-

مواصفات البطارية A23 وتوافقها

بطارية A23 عبارة عن بطارية صغيرة على شكل أسطوانة مع جهد عالي.يُطلق عليه أيضًا 23a أو 23ae أو Mn21 ، ويتم تشغيله بسرعة 12 فولت وأعلى بكثير من بطاريات AA أو AAA.تصميمه الخاص يجعلها مثالية لل...على 01/01/1970 52215