XC2C256-7TQ144C CPLD: Pinout ، الميزات ، دليل برمجة ورقة البيانات

في هذا الدليل ، ستحصل على نظرة واضحة على XC2C256-7TQ144C ، وهو CPLD منخفض الطاقة من عائلة Coolrunner-II في Xilinx (الآن AMD).ستتعرف على تكوين PIN ، ونماذج CAD ، والميزات الرئيسية مثل سعة المنطق ، وخيارات الإدخال/الإخراج ، ودعم الجهد ، ووظائف توفير الطاقة.سنقوم أيضًا بالمرور من خلال بنيةها ، ومنحنى I/V ، والمواصفات ، تليها التطبيقات ، والأجزاء المماثلة ، وخطوات البرمجة ، والمزايا والعيوب ، وتفاصيل التغليف ، ومعلومات الشركة المصنعة حتى تتمكن من فهم كيفية ملاءمة هذا الجهاز مع مشاريعك بالضبط.كتالوج

ما هو XC2C256-7TQ144C؟

ال XC2C256-7TQ144C هو جهاز CPLD منخفض الطاقة (جهاز منطقي قابل للبرمجة معقد) من عائلة CoolRunner-II من Xilinx ، وهو الآن جزء من AMD.إنه يتميز بـ 256 Macrocells ويأتي في حزمة TQFP 144 دبوس ، مصممة للتشغيل السريع والحتمي مع الحد الأدنى من استهلاك الطاقة.تعمل على CORE 1.8 فولت ، فهو يوفر أداءً موثوقاً به في عامل شكل مضغوط وهو مناسب تمامًا للتصميمات التي تتطلب القدرة الفورية وتنفيذ المنطق الفعال.كجزء من سلسلة CoolRunner-II متعددة الاستخدامات ، تستفيد من بنية مجربة وتوافق التصميم الواسع.

هل تبحث عن XC2C256-7TQ144C؟اتصل بنا للتحقق من الأسهم الحالية ، وتهمة المهلة ، والتسعير.

XC2C256-7TQ144C DIAGRAM

يوضح الرسم البياني XC2C256-7TQ144C Pin-Out كيفية ترتيب دبابيس 144 للحصول على وظائف I/O للبرمجة.معظم المسامير هي I/O ، والتي يمكن تكوينها كمدخلات أو مخرجات ، ويتم توزيعها بالتساوي لدعم التوجيه المرن.يتم وضع دبابيس VCC و VCCIO1 و VCCIO2 و VAUX و GND حول الحزمة لتوفير توزيع طاقة مستقر وخيارات جهد I/O متعددة.يتم تجميع دبابيس JTAG (TDI ، TDO ، TMS ، TCK) معًا لسهولة البرمجة والاختبار في النظام.

XC2C256-7TQ144C CAD نماذج

XC2C256-7TQ144C رمز

XC2C256-7TQ144C بصمة

XC2C256-7TQ144C 3D نموذج

XC2C256-7TQ144C ميزات

• نوع الجهاز والأسرة

XC2C256-7TQ144C هو جهاز منطقي قابل للبرمجة (CPLD) ينتمي إلى عائلة CoolRunner-II التي طورتها Xilinx (الآن AMD).إنه مصمم لاستهلاك الطاقة المنخفضة مع الحفاظ على أداء منطقي سريع وحتمي ، مما يجعله مثاليًا للتطبيقات المنطقية والتواصل.

• القدرة المنطقية

يحتوي هذا الجهاز على 256 Macrocells ، وهي موارد المنطق القابلة للبرمجة في CPLD.يمكن تكوين هذه الكواكيل لتنفيذ مختلف وظائف المنطق التوافقي والتسلسل ، مما يعطي قدرة معتدلة للتحكم ، ومنطق الغراء ، وواجهات الحافلات.

• كتل المنطق (كتل الوظائف)

يدمج 16 كتل وظائف تنظم وإدارة مجموعات من macrocells.يوفر كل كتلة موارد متداخلة وموارد محلية للمنتج ، مما يتيح تنفيذ المنطق المرن والتوجيه الفعال داخل الجهاز.

• دبابيس I/O المستخدم

يوفر XC2C256-7TQ144C ما يصل إلى 118 دبابيس إدخال/إخراج قابلة للتكوين في حزمة TQFP-144.يمكّن عدد الدبوس العالي هذا الجهاز من التواصل مع أنظمة فرعية متعددة في وقت واحد ، مما يجعله مناسبًا للتصاميم المعقدة على مستوى اللوحة.

• الجهد الأساسي (VCC)

يعمل Core عند 1.8 V (1.7 V إلى 1.9 فولت نطاق) ، مما يساعد على تقليل استهلاك الطاقة مقارنةً بـ 5 V V CPLDs الأقدم.هذا الجهد السفلي مفيد في الأنظمة الرقمية الحديثة المختلطة.

• دعم I/O متعدد الجهد

تدعم البنوك I/O معايير الجهد المتعددة بما في ذلك 1.5 فولت و 1.8 فولت و 2.5 فولت و 3.3 فولت. تتيح هذه المرونة لـ CPLD الواجهة مباشرة مع المكونات التي تعمل بمستويات مختلفة من الجهد بدون محفزات مستوية خارجية.

• عملية عالية السرعة

من خلال تأخير انتشار دبوس إلى دبوس من حوالي 5.7 نانو ثانية (الصف السرعة "-7") ، يقدم الجهاز أداءً سريعًا وحتميًا.هذا يجعلها مناسبة للتطبيقات المهمة التوقيت مثل فك تشفير العناوين ، وتحكيم الحافلات ، والسيطرة.

• استهلاك الطاقة المنخفض

تشتهر سلسلة CoolRunner-II لتيارات الاحتياطية المنخفضة للغاية ، وغالبًا ما تكون في نطاق Microamp.تتيح هذه الطاقة الثابتة المنخفضة ، جنبًا إلى جنب مع ميزات توفير الطاقة الديناميكية ، استخدام XC2C256-7TQ144C بشكل فعال في الأنظمة التي تعمل بالبطارية أو دائمًا.

• تقنية Datagate

تتيح هذه الميزة من إخراج المدخلات غير المستخدمة ، مما يمنع التبديل غير الضروري وتقليل استهلاك الطاقة الديناميكي.إنها قيمة في التطبيقات التي تكون فيها إشارات معينة غير نشطة لفترات طويلة.

• برمجة JTAG في النظام

يدعم الجهاز IEEE 1149.1 (JTAG) و IEEE 1532 للبرمجة داخل النظام.هذا يعني أنه يمكن تكوين CPLD واختباره وإعادة برمجته دون إزالته من اللوحة ، وتبسيط التطوير والتحديثات.

• هيكل التسجيل المتقدم

يشمل XC2C256-7TQ144C ساعات عالمية متعددة ، وفواصل على مدار الساعة ، والسجلات المزدوجة التي يتم تشغيلها.كما يوفر مجموعة/إعادة تعيين عالمية وتجهيز محلي لكل ماكروسيل ، مما يعطي تحكمًا مرنًا في التوقيت والمزامنة.

• مدخلات Schmitt-trigger

يمكن تهيئة دبابيس الإدخال المحددة كما يطلق Schmitt لتحسين مناعة الضوضاء.هذا مفيد للتعامل مع إشارات الإدخال البطيئة أو الصاخبة دون إضافة دائرة تكييف خارجية.

• ميزات الإخراج المرنة

تدعم المخرجات التشغيل من ثلاث حالات ، والتحكم في أسعار الفائدة ، وتكوينات الحافلة ، والتكوينات المفتوحة ، والسحب الاختياري.تجعل هذه الخيارات من السهل تكييف CPLD مع معايير الحافلات المختلفة وظروف الحمل الخارجية.

• المصفوفة المتقدمة المتقدمة (الهدف)

تربط مصفوفة المصفوفة المتقدمة بفعالية من كتل الوظائف ، مما يوفر توجيهًا كاملًا للمنتج عبر الجهاز.هذا يعمل على تحسين مرونة المنطق في المنطق ويساعد على الحفاظ على أداء التوقيت المتوقع.

العمارة Coolrunner-II CPLD

تم بناء بنية CoolRunner-II CPLD من XC2C256-7TQ144C حول كتل الوظائف ، وكتل I/O ، ومصفوفة متطورة ربط (AIM).تحتوي كل كتلة دالة على macrocells ومجموعة منطق قابلة للبرمجة (PLA) تنفذ المنطق المعرفة من قبل المستخدم ، في حين أن الهدف يوجه إشارات بين الكتل.إن إدخال/إخراج يحظر واجهة المنطق الداخلي مع دبابيس خارجية ، ودعم دوائر JTAG و BSC/ISP المخصصة.تتيح هذه الهندسة المعمارية المهيكلة والمترابطة أداءً سريعًا وحتميًا مع انخفاض استهلاك الطاقة ، مما يجعله مثاليًا للتحكم والتواصل والغراء في الأنظمة الرقمية.

منحنى I/V النموذجي لـ XC2C256

يوضح منحنى I/V النموذجي لـ XC2C256-7TQ144C العلاقة بين جهد الإخراج (VO) وتيار المخرجات (IO) لمختلف فولتية إمداد I/O (1.5 فولت ، 1.8 فولت ، 2.5 فولت ، و 3.3 فولت).مع زيادة جهد الإمداد ، يمكن للجهاز مصدر أو تغرق التيارات الأعلى قبل أن يبدأ جهد الخرج في الانخفاض بشكل كبير.هذا السلوك مهم لفهم قدرة محرك الأقراص على CPLD عند التواصل مع المكونات الخارجية ، مما يضمن أن مستويات الإشارة صالحة تحت الحمل.يستخدم الكثيرون هذا المنحنى لتحديد فولتية الإدخال/الإخراج المناسبة وضمان تشغيل موثوق في التطبيقات التي تتطلب نقاط قوة محددة في القيادة الحالية.

XC2C256-7TQ144C المواصفات

|

يكتب |

المعلمة |

|

الشركة المصنعة |

AMD/Xilinx |

|

مسلسل |

Coolrunner II |

|

التغليف |

صينية |

|

حالة الجزء |

عفا عليها الزمن |

|

نوع قابل للبرمجة |

في النظام قابل للبرمجة |

|

تأخير وقت TPD (1) كحد أقصى |

6.7 ns |

|

إمدادات الجهد - داخلي |

1.7 V ~ 1.9 V |

|

عدد العناصر/الكتل المنطقية |

16 |

|

عدد macrocells |

256 |

|

عدد البوابات |

6000 |

|

عدد i/o |

118 |

|

درجة حرارة التشغيل |

0 درجة مئوية ~ 70 درجة مئوية (TA) |

|

نوع التثبيت |

جبل السطح |

|

حزمة / حالة |

144-LQFP

|

|

حزمة جهاز المورد |

144-TQFP (20 × 20) |

|

رقم المنتج الأساسي |

XC2C256 |

XC2C256-7TQ144C تطبيقات

1. منطق الغراء والواجهة سد

يعد XC2C256-7TQ144C مثاليًا لتنفيذ منطق الغراء ، والذي يربط الإشارات وتنسيقها بين المكونات الرقمية المختلفة.يمكنه التعامل مع وظائف مثل فك تشفير العناوين ، وتحكيم الحافلات ، وترجمة البروتوكول ، مما يتيح التواصل السلس بين متحكمهم ، والذاكرة ، وأجهزة الاستشعار ، وغيرها من الأجهزة الطرفية.يضمن توقيته المتوقع والتأخير السريع للدخول إلى دبوس التواصل الموثوق به حتى في تصميمات اللوح المعقدة.

2. أجهزة منخفضة الطاقة والبطارية

بفضل تقنية Fast Zero Power (FZP) والتيار المنخفض للغاية ، يعد هذا CPLD مناسبًا للغاية للإلكترونيات المحمولة والبطارية.يمكن أن تظل تعمل بشكل مستمر أثناء استهلاك الحد الأدنى من الطاقة ، مما يجعلها مثالية لدوائر التحكم أو المراقبة دائمًا.يمكنك تقليل استخدام الطاقة بشكل أكبر مع ميزات مثل Datagate ، والتي تقلل من التبديل الديناميكي عندما تكون المدخلات غير نشطة.

3. المنطق والتوصيل

يتفوق الجهاز في تطبيق آلات الحالة المحدودة ، والتحكم في التوقيت ، وتسلسل الإشارة المطلوبة في العديد من الأنظمة المضمنة.تتيح بنيةها الحتمية غير المتطايرة أن يصبح منطق التحكم نشطًا فور زيادة الطاقة دون تأخير التكوين.هذا يجعله خيارًا قويًا لإعادة تعيين المنطق ، ودوائر المصافحة ، وغيرها من مهام التحكم في الوقت المحدد.

4. دعم النظام المدمج والمنطق المحيطي

في التصميمات المدمجة ، يمكن لـ XC2C256-7TQ144C أن يكون بمثابة شريحة دعم قابلة للتخصيص ، أو تنفيذ واجهات متخصصة أو توسيع قدرات متحكم.يمكنه التعامل مع بروتوكولات الاتصال مثل SPI أو I²C أو UART ، أو إنشاء تحديد رقائق ، أو إدارة توجيه المقاطعة.من خلال تفريغ هذه الوظائف من وحدة المعالجة المركزية ، فإنه يبسط تطوير البرامج الثابتة ويحسن أداء النظام بشكل عام.

XC2C256-7TQ144C أجزاء مماثلة

|

مواصفة |

XC2C256-7TQ144C |

XC2C256-7TQ144I |

XC2C256-7TQG144I |

XC2C256-7VQ100C |

XC2C256-7VQG100C |

XC2C256-6TQ144C |

|

عائلة الجهاز |

coolrunner-ii cpld |

coolrunner-ii cpld |

coolrunner-ii cpld |

coolrunner-ii cpld |

coolrunner-ii cpld |

coolrunner-ii cpld |

|

كثافة المنطق (macrocells) |

256 |

256 |

256 |

256 |

256 |

256 |

|

نوع الحزمة |

TQFP-144 |

TQFP-144 |

TQFP-144 (خالية من PB) |

VQFP-100 |

VQFP-100 (خالية من PB) |

TQFP-144 |

|

درجة السرعة |

-7 |

-7 |

-7 |

-7 |

-7 |

-6 (أسرع) |

|

نطاق درجة الحرارة |

تجاري (0 - 70 درجة مئوية) |

الصناعي (-40-85 درجة مئوية) |

الصناعي (-40-85 درجة مئوية) |

تجاري (0 - 70 درجة مئوية) |

تجاري (0 - 70 درجة مئوية) |

تجاري (0 - 70 درجة مئوية) |

|

عدد دبوس I/O. |

118 |

118 |

118 |

80 |

80 |

118 |

|

الجهد الأساسي (VCC) |

1.8 v |

1.8 v |

1.8 v |

1.8 v |

1.8 v |

1.8 v |

|

دعم الجهد I/O. |

1.5 V - 3.3 V |

1.5 V - 3.3 V |

1.5 V - 3.3 V |

1.5 V - 3.3 V |

1.5 V - 3.3 V |

1.5 V - 3.3 V |

|

الامتثال / خالية من PB |

معيار |

معيار |

PB خالية / ROHS |

معيار |

PB خالية / ROHS |

معيار |

|

الاختلافات |

النسخة التجارية الأساسية |

نسخة مؤقتة صناعية |

نسخة صناعية + PB خالية |

حزمة أصغر ، أقل من I/O |

نسخة أصغر خالية من PB |

نسخة توقيت أسرع |

XC2C256-7TQ144C خطوات البرمجة

برمجة XC2C256-7TQ144C هي عملية واضحة تتضمن إعداد التصميم الخاص بك وإنشاء ملف البرمجة وتحميله في CPLD عبر JTAG.باتباع كل خطوة بعناية ، يمكنك التأكد من تكوين ناجح وتشغيل الجهاز المناسب على اللوحة.

1. التصميم والتوليف

تبدأ بكتابة تصميم المنطق الخاص بك باستخدام HDL (VHDL أو Verilog) أو الإدخال التخطيطي.بعد الانتهاء من التصميم ، تقوم بتشغيل عملية التوليف ، التي تحول منطقك إلى التركيب الداخلي للجهاز من macrocells والترابط.تضمن هذه الخطوة أن التصميم الخاص بك متوافق مع بنية XC2C256 وجاهزة للتنفيذ.

2. المكان والطريق / التنفيذ (المناسب)

بعد ذلك ، يمكنك أداء Place and Route ، المعروف أيضًا باسم Fitting ، والذي يعين منطقك المصنوع إلى المقطع الكلي الفعلي الفعلي وموارد التوجيه داخل CPLD.تتحقق الأداة من قيود التوقيت ، وتحل استخدام الموارد ، وتحسن المسارات لتلبية أداء التصميم الخاص بك.هذا يضمن أن الدائرة ستعمل بشكل موثوق بمجرد برمجة الجهاز.

3. إنشاء ملف البرمجة

بمجرد اكتمال التنفيذ ، تقوم بإنشاء ملف البرمجة (تنسيق Bit أو JAM أو SVF) الذي يحتوي على بيانات التكوين الدقيقة للجهاز.يمثل هذا الملف كيف يتم إعداد كل macrocell و interconnect و I/O لتنفيذ منطقك.هناك حاجة إلى إعداد هذا الملف قبل الانتقال إلى برمجة الجهاز الفعلية.

4. برمجة JTAG / في النظام

أخيرًا ، تقوم بتوصيل الجهاز بجهاز الكمبيوتر الخاص بك باستخدام كبل برمجة JTAG وفتح أداة تأثير Xilinx (أو ما يعادلها).يمكنك بعد ذلك تحميل ملف البرمجة الذي تم إنشاؤه وتنزيله على XC2C256-7TQ144C من خلال دبابيس JTAG (TDI ، TDO ، TCK ، TMS).بمجرد اكتمال العملية ، يبدأ CPLD على الفور في العمل مع المنطق المبرمج ، دون الحاجة إلى دورة طاقة أو ذاكرة تكوين خارجية.

XC2C256-7TQ144C مزايا وعيوب

المزايا

• قوة الاستعداد منخفضة للغاية ، مثالية للتصميمات التي تعمل بالبطاريات.

• التشغيل الفوري مع عدم وجود تأخير التكوين.

• توقيت يمكن التنبؤ به لسهولة إغلاق التصميم.

• يحل محل رقائق المنطق المتعددة المنفصلة ، وتوفير المساحة والتكلفة.

• يدعم الفولتية I/O متعددة دون محولات المستوى الخارجي.

عيوب

• سعة المنطق المحدودة مقارنة مع CPLDs الأكبر أو FPGAs.

• لا يوجد DSP مدمج أو ذاكرة الوصول العشوائي أو أجهزة الإرسال والاستقبال عالية السرعة.

• تصبح عفا عليها الزمن ، مما يجعل المصادر في المستقبل أكثر صعوبة.

• انخفاض السقف الأداء للتطبيقات عالية السرعة.

• مرونة توجيه أقل للتصميمات المعقدة أو غير المنتظمة.

XC2C256-7TQ144C أبعاد التغليف

|

يكتب |

المعلمة |

|

نوع الحزمة |

TQFP-144 |

|

الحزمة حجم الجسم |

20 مم × 20 مم |

|

الرصاص الملعب |

0.5 مم |

|

عدد المسامير |

144 |

|

ارتفاع الحزمة (الحد الأقصى) |

1.4 مم |

|

سمك الحزمة (الاسمية) |

1.0 مم |

|

طول الرصاص |

0.45 مم ~ 0.75 مم |

|

عرض الرصاص |

0.17 مم ~ 0.27 مم |

|

نوع التثبيت |

جبل السطح |

|

حزمة جهاز المورد |

144-TQFP (20 × 20) |

XC2C256-7TQ144C الشركة المصنعة

يتم تصنيع XC2C256-7TQ144C بواسطة Xilinx، شركة رائدة في حلول المنطق القابلة للبرمجة.تم التعرف على Xilinx على نطاق واسع لتقنيات FPGA و CPLD الرائدة ، مما يوفر أجهزة موثوقة وعالية الأداء للتطبيقات الصناعية والتجارية والمستهلكين.اليوم ، يعمل Xilinx كجزء من AMD، الاستمرار في تقديم منتجات منطقية قابلة للبرمجة متقدمة بدعم قوي طويل الأجل والابتكار.

خاتمة

تبرز XC2C256-7TQ144C لاستهلاكها المنخفض للطاقة ، والأداء الحتمي السريع ، ومرونة I/O متعددة الجهد ، مما يجعلها خيارًا موثوقًا للتصميمات الرقمية الحديثة.مزيجها المتوازن من 256 Macrocells ، 118 دبابيس I/O ، والهندسة المعمارية المتقدمة المتقدمة تدعم مجموعة واسعة من وظائف المنطق والتواصل والغراء.بدعم من البرمجة داخل النظام ، وميزات Datagate لتوفير الطاقة ، وتكوينات الإدخال/الإخراج القوية ، فإنها تدمج بسلاسة في أنظمة مضمنة وبيئات الجهد المختلط.

ورقة البيانات pdf

XC2C256-7TQ144C أوراق البيانات:

معلومات عنا

ALLELCO LIMITED

قراءة المزيد

تحقيق سريع

الرجاء إرسال استفسار ، وسوف نرد على الفور.

أسئلة مكررة [FAQ]

1. هل تتطلب XC2C256-7TQ144C ذاكرة التكوين الخارجي؟

لا. إحدى مزاياها هي التشغيل الفوري.يتم تخزين التكوين داخليًا ، لذلك يعمل على استعداد للتشغيل دون أي حفلة موسيقية خارجية أو ذاكرة فلاش.

2. ما هي أدوات البرمجة المتوافقة مع XC2C256-7TQ144C؟

يمكنك برمجة الجهاز باستخدام برنامج Xilinx Impact مع كبل برمجة JTAG.يستخدم الكثيرون أيضًا مبرمجي JTAG المتوافقة مع معايير IEEE 1149.1/1532.

3. هل يمكن لـ XC2C256-7TQ144C استبدال ICS متعددة المنطق المنطقي في التصميم الخاص بك؟

نعم.من خلال 256 Macrocells و I/O المرنة ، يمكن لـ CPLD دمج العديد من وظائف المنطق والتحكم في أجهزة واحدة ، مما يساعدك على تقليل مساحة اللوحة وعدد المكونات.

4. هل XC2C256-7TQ144C مناسب لتطبيقات البطارية منخفضة الطاقة؟

نعم.بفضل تقنية Fast Zero Power (FZP) والتيار المنخفض للغاية ، فهي مثالية للدوائر التي تعمل دائمًا والأجهزة المحمولة والأنظمة المضمنة الحساسة للطاقة.

5. هل يمكنك استخدام XC2C256-7TQ144C لمعالجة الإشارات عالية السرعة؟

إنه غير مصمم لمهام DSP عالية السرعة أو مهام جهاز الإرسال والاستقبال.على الرغم من أنه يقدم تأخيرات سريعة الدبوس إلى دبوس ، إلا أنه مناسبة للتحكم والتواصل والتوقيت ، وليس معالجة البيانات المعقدة.

EP2S60F672C4 FPGA: الميزات والتطبيقات والبرمجة ودليل ورقة البيانات

على 04/10/2025

EPM3256AFC256-7 نظرة عامة على CPLD: الميزات ، pinout ، البرمجة والتطبيقات

على 03/10/2025

الوظائف الشعبية

-

أجهزة الكمبيوتر المعقدة لتعليمات التعليمات: كيف غيرت الحوسبة؟

على 19/04/8000 147781

-

usb-c pinout والميزات

على 19/04/2000 112056

-

باستخدام بدائل المحاكاة الموحدة Xilinx: دليل شامل لتصميم ومحاكاة FPGA

على 19/04/1600 111352

-

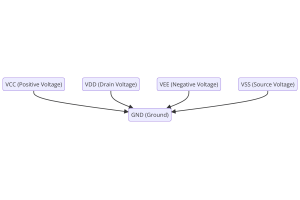

جهد مصدر الطاقة في الإلكترونيات: معنى VCC، VDD، VEE، VSS، وGND

على 19/04/0400 83811

-

دليل موصل RJ45: pinout ، الأسلاك ، أنواع الكابلات ، والاستخدامات

على 01/01/1970 79624

-

الدليل النهائي لرموز الألوان السلكية في الأنظمة الكهربائية الحديثة

الطريقة التي تستخدمها أنظمةنا الكهربائية بالألوان ليست فقط للمظهر.يشير كل لون سلك الآن إلى وظيفة محددة ، مما يسهل تحديد المكونات الكهربائية والتعامل معها بشكل صحيح أثناء التثبيت والصيانة.هذا لا يسر...على 01/01/1970 66995

-

دليل Purge Valve: الوظيفة والأعراض والاختبار والاستبدال لأداء المحرك الأمثل

يعد Purge Valve جزءًا رئيسيًا من نظام السيارة الذي يساعد في الحفاظ على نظافة الهواء من خلال إدارة أبخرة الوقود قبل أن يتمكنوا من الهروب إلى الجو.هذا لا يساعد البيئة فقط عن طريق تقليل التلوث ولكن أي...على 01/01/1970 63119

-

الجودة (س) العامل: المعادلات والتطبيقات

يعد عامل الجودة ، أو "Q" مهمًا عند التحقق من مدى عمل المحاثات والراتين في الأنظمة الإلكترونية التي تستخدم ترددات الراديو (RF).يقيس "Q" مدى تقليل الدائرة إلى تقليل فقدان الطاقة وتؤثر على نطاق التردد...على 01/01/1970 63057

-

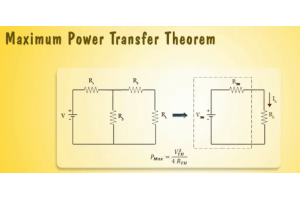

تحقيق ذروة أداء مع أقصى نظرية نقل الطاقة

تشرح نظرية نقل الطاقة القصوى كيف تتدفق الطاقة من مصدر ، مثل البطارية أو المولد ، إلى الحمل المتصل.يوضح الحالة الدقيقة التي يتلقى فيها الحمل أكثر الطاقة.تغطي هذه المقالة ما تعنيه النظرية ، وكيف تعمل...على 01/01/1970 54097

-

مواصفات البطارية A23 وتوافقها

بطارية A23 عبارة عن بطارية صغيرة على شكل أسطوانة مع جهد عالي.يُطلق عليه أيضًا 23a أو 23ae أو Mn21 ، ويتم تشغيله بسرعة 12 فولت وأعلى بكثير من بطاريات AA أو AAA.تصميمه الخاص يجعلها مثالية لل...على 01/01/1970 52207