LC5768MC-75F256C CPLD: الميزات والمواصفات والمزايا والتطبيقات

يشرح هذا الدليل LC5768MC-75F256C ، وهي شريحة صغيرة ولكنها قوية مصنوعة من أشباه الموصلات.إنه يوضح ما تفعله الشريحة ، وكيفية عملها ، وكيفية برمجتها ، وأين يمكن استخدامها.إذا كنت تبحث عن شريحة تتعامل مع المهام المنطقية ، وتستخدم الطاقة المنخفضة ، وتعمل في العديد من الأجهزة ، سيساعدك هذا الدليل على فهم سبب كون LC5768MC-75F256C خيارًا جيدًا.كتالوج

ما هو LC5768MC-75F256C؟

ال LC5768MC-75F256C هو جهاز منطقي قابل للبرمجة قابلة للبرمجة (CPLD) ، وهو جزء من عائلة ISPXPLD 5000MC.تم تصميم هذا الجهاز حول بنية Core Core 1.8 فولت ويوفر كثافة منطقية قوية ، ودمج 768 Macrocells.بصفته عضوًا في سلسلة 5000mc ، فإنه يمثل حلول CPLD المتقدمة من Lattice والتي توفر التحكم في توقيت موثوق ، وتنفيذ منطقي فعال ، وتشغيل منخفض للطاقة ، وكلها تم تحسينها للأنظمة الرقمية المضمنة وعالية السرعة.تعزز عائلة ISPXPLD 5000MC قدرات CPLDs التقليدية من خلال إدخال كتل متعددة الوظائف (MFBS) ودعم I/O المرن ، مما يجعل LC5768MC-75F256C اختيارًا قويًا للتكامل المنطقي القابل للتطوير.بفضل موثوقيتها وبنته المصممة خصيصًا للأداء الحتمي ، يعمل هذا الجهاز كحبة بناء يمكن الاعتماد عليها في التصميم الرقمي.

هل تبحث عن LC5768MC-75F256C؟اتصل بنا للتحقق من الأسهم الحالية ، وتهمة المهلة ، والتسعير.

LC5768MC-75F256C ميزات

• 768 Macrocells (الهندسة المعمارية المستندة إلى MFB)

يدمج الجهاز 768 Macrocells المنظمة في كتل متعددة الوظائف متقدمة (MFBs) ، مما يدعم منطقًا عالي الكثافة مع قدرات الحساب والذاكرة المضمنة.تسمح هذه MFBs بتكوين مرن للمنطق و SRAM-Port SRAM و FIFO و CAM.

• الجهد الأساسي 1.8V (متغير MC)

يعمل متغير MC-Series مع قلب 1.8 فولت ، ويوفر استهلاكًا أقل للطاقة لتصميمات محمولة وعالية الكفاءة.على الرغم من انخفاض الجهد ، فإنه يحافظ على أداء قوي وكثافة المنطق.

• 7.5 تأخير انتشار NS (الصف السرعة -75)

إنه يحقق تأخير انتشار أقصى دبوس إلى دبوس قدره 7.5 نانو ثانية فقط ، مما يجعله مناسبًا للتطبيقات الرقمية المعتدلة إلى عالية السرعة.ترجع درجة السرعة -75 قوة وسرعة في الأنظمة المدمجة.

• 193 دبابيس I/O قابلة للبرمجة

توفر الشريحة 193 دبابيس I/O تدعم معايير وبروتوكولات الجهد المتعددة.هذه المسامير قابلة للبرمجة بالكامل وتسمح بتواصل مرن مع الأجهزة المنطقية أو التناظرية الأخرى.

• دعم المنطق الفائق (ما يصل إلى 136 مدخلًا لكل كتلة)

يدعم كل MFB وظائف منطقية واسعة جدًا مع ما يصل إلى 136 إشارات إدخال ، مما يتيح منطقًا تواصلًا معقدًا في مستويات منطقية أقل.هذا يقلل من تأخير الانتشار ويبسيط تخليق المنطق.

• SRAM ، SRAM ، FIFO ، FIFO ، ودعم الكاميرا الثلاثية

MFBs قابلة للتكوين لتكون بمثابة SRAM (منفذ واحد/مزدوج) ، أو FIFOS ، أو محتوى ثلاثي الذاكرة المعالجة.تتيح هذه المرونة تصميم المنطق الغني بالذاكرة في CPLD مدمجة.

• على الرقاقة PLL (SysClock ™)

يدعم PLL المدمج مضاعفة/تقسيم الساعة من 1 × إلى 32 × ، وتغيير الطور ، والتعليقات الخارجية.يساعد في إدارة التوقيت والانحراف عبر الأنظمة المتزامنة عالية السرعة.

• الدعم القياسي الإدخال/الإخراج الواسع (Sysio ™)

تدعم كتل I/O مجموعة واسعة من معايير الإشارات بما في ذلك LVCMOS و LVTTL و SSTL و HSTL و GTL+و LVDS و LVPECL.هذا يتيح الجهد المختلط والإشارة التفاضلية على جهاز واحد.

• قابلية البرمجة داخل النظام (ISPXP ™)

يدعم الجهاز البرمجة داخل النظام من خلال واجهة IEEE 1532 أو SysConfig.يمكن إعادة برمجتها على السبورة دون إزالتها ، وتمكين تحديثات التصميم وإعادة تكوين المجال.

• اختبار مسح الحدود (IEEE 1149.1 متوافق)

يتيح دعم المسح الضوئي الكامل JTAG إجراء اختبار قوي على مستوى اللوحة وتصحيح الأخطاء.وهذا يضمن الامتثال لمتطلبات الاختبار الحديثة وتبسيط التحقق من الصحة في الإنتاج.

• 5V متسامح I/O.

على الرغم من النواة 1.8 فولت ، فإن ضفاف الإدخال/الإخراج تتسامح مع إشارات 5 فولت ، مما يدعم واجهات الجهد القديمة.هذا يحسن التوافق مع الأنظمة القديمة وبيئات الجهد المختلط.

مخطط كتلة ISPXPLD 5000MX/5000MC

يسلط مخطط الكتلة لعائلة LC5768MC-75F256C في عائلة ISPXPLD 5000MX/5000MC إلى كيفية تنظيم الشريحة للتعامل مع المهام المنطقية القابلة للبرمجة.يوجد في المركز مجموعة التوجيه العالمية (GRP) ، والتي تعمل كمحور اتصال رئيسي ، وربط مختلف الكتل المنطقية والوظيفية بحيث يمكن للإشارات أن تتحرك بكفاءة في جميع أنحاء الجهاز.على جانبي GRP توجد حلقتين محفوظة للمرحلة (PLL0 و PLL1) ، جزء من نظام SysClock.هذه تولد إشارات ساعة دقيقة وقابلة للتعديل تساعد على الحفاظ على دقة التوقيت للعمليات عالية السرعة عبر الشريحة.

حول GRP و PLLs أربعة بنوك Sysio.يحتوي كل بنك على صفائف نظام قابلة للتكوين (CSAs) وكتل متعددة الوظائف (MFBs).تتعامل CSAs مع معالجة المنطق الأساسي ، بينما تدعم MFBS ميزات أكثر تقدمًا مثل عمليات الرياضيات ووظائف الذاكرة.يمنح هذا الترتيب الجهاز مرونة I/O قوية ويسهل توسيع نطاق التطبيقات المختلفة.وتوصيلات الطاقة والساعة تظهر بوضوح في الرسم البياني.يتم توزيع دبابيس VCC و VREF و GND المتعددة للحفاظ على الطاقة المستقرة عبر الشريحة.تتيح مدخلات الساعة العالمية (GCLK0 إلى GCLK3) الساعات الخارجية للتغذية في النظام والعمل مع GRP و PLLs.

مخطط كتلة متعدد الوظائف (MFB)

يجمع الكتلة متعددة الوظائف (MFB) في LC5768MC-75F256C ISPXPLD 5000MX/5000MC بين كل من وظائف الذاكرة والمنطق لدعم احتياجات التصميم المرنة.وهو يدعم العديد من أنواع الذاكرة ، بما في ذلك RAM Dual Port RAM (8،192 بت) ، وذاكرة الوصول المزدوجة المزدوجة ، FIFO ، وذاكرة الوصول العشوائي المفردة (كل ما يصل إلى 16،384 بت) ، بالإضافة إلى الكاميرا الثلاثية (128 × 48).تجعل خيارات الذاكرة هذه MFB مفيدة للتخزين المؤقت للبيانات ، والتخزين المؤقت ، والبحث السريع عن البيانات.

MFB أيضا لديه قدرات منطقية قوية.ويشمل 68 مدخلات من مصفيف مصطلح 164 منتج و 32 macrocells ، مما يسمح لها بإجراء عمليات منطقية معقدة.يستخدم مدخلات على مدار الساعة (CLK0 إلى CLK3) وإشارة إعادة تعيين للتحكم في التوقيت والعمليات.لتوسيع الوظائف ، تتيح المنافذ المتتالية في/الخارج توصيل MFBs معًا عبر الكتل.تقوم واجهة QSA (صفيف نظام Quad) بتوصيل MFB إلى البنوك I/O للاتصال السريع مع الأنظمة الخارجية.باختصار ، تعد MFB وحدة قوية ومرنة تتعامل مع كل من المهام والمنطق ، مما يساعد الجهاز على الأداء بشكل جيد في التطبيقات المضمنة وعالية السرعة.

LC5768MC-75F256C المواصفات

|

يكتب |

المعلمة |

|

الشركة المصنعة |

شعرية Semiconductor Corporation |

|

مسلسل |

ISPXPLD® 5000 |

|

التغليف |

حجم كبير |

|

حالة الجزء |

نشيط |

|

نوع قابل للبرمجة |

في النظام قابل للبرمجة |

|

تأخير وقت TPD (1) كحد أقصى |

7.5 ns |

|

إمداد الجهد - داخلي |

1.65V ~ 1.95V |

|

عدد العناصر/الكتل المنطقية |

24 |

|

عدد macrocells |

768 |

|

عدد i/o |

193 |

|

درجة حرارة التشغيل |

0 درجة مئوية ~ 90 درجة مئوية (TJ) |

|

نوع التثبيت |

جبل السطح |

|

حزمة / حالة |

256-BGA |

|

حزمة جهاز المورد |

256-FPBGA (17x17) |

LC5768MC-75F256C تطبيقات

1. الاتصالات السلكية واللاسلكية والشبكات

يعد LC5768MC-75F256C مثاليًا للاستخدام في المحطات الأساسية ، ومفاتيح الاتصالات ، ووحدات الشبكة البصرية ، حيث هناك حاجة إلى المنطق عالي السرعة والمنطق الحتمي.تمكين ذاكرتها المدمجة ودعم I/O متعدد الجهد تمكين معالجة البروتوكول ، وإطار البيانات ، ومهام التحكم في الكلية المنخفضة.

2. اتصال البيانات وتخزينها

هذا CPLD مناسب تمامًا لأجهزة التوجيه ووحدات التحكم في RAID وأنظمة صفيرة القرص التي تتطلب معالجة بيانات فعالة ومعالجة إشارات سريعة.يوفر دعم SRAM ثنائي المنفذ و FIFO التحكم في التخزين المؤقت والتحكم في التدفق في البيئات عالية الإنتاجية.

3. معالجات البروتوكول وواجهات الحافلات

مع توقيت يمكن التنبؤ به وموارد المنطق عالية الكثافة ، يتفوق LC5768MC في تنفيذ جسور الحافلات ، وواجهات الطائرة الخلفية ، وفكات البروتوكول.إنه يتيح الاستجابات المنطقية السريعة ويدعم تكاملًا سلسًا مع معايير إشارات متعددة.

4. أنظمة التحكم الصناعية وإنترنت الأشياء

في الأتمتة الصناعية ، يتم استخدام الجهاز للمراقبة والتحكم في الماكينة وتسلسل المنطق.إن قدرتها الفورية ، وسحب الطاقة المنخفضة ، وميزات الإدخال/الإخراج القوية تجعلها مناسبة لعقد إنترنت الأشياء ووحدات التحكم المضمنة.

5. إلكترونيات المستهلك والطبية

إن البصمة المدمجة وقدرات الذاكرة المنطقية الغنية تجعل هذا CPLD قيمة في الأدوات الطبية المحمولة والإلكترونيات الاستهلاكية.إنه يتعامل مع التحكم في النظام ، وإدارة الواجهة ، وتسلسل الطاقة في التصميمات المقيدة بالحجم والحساسة للطاقة.

LC5768MC-75F256C أجزاء مماثلة

|

ميزة |

LC5768MC-75F256C |

LC5768MV-75F484C |

LC5768MV-75FN256C |

LC5768MV-5F484C |

|

عائلة |

ISPXPLD 5000MC |

ISPXPLD 5000MV |

ISPXPLD 5000MV |

ISPXPLD 5000MV |

|

الجهد الأساسي |

1.8 فولت |

3.3V |

3.3V |

3.3V |

|

macrocells |

768 |

768 |

768 |

768 |

|

التردد القصوى |

~ 150MHz |

~ 150MHz |

~ 150MHz |

~ 200-250MHz |

|

تأخير الانتشار (TPD) |

7.5ns |

7.5ns |

7.5ns |

5ns |

|

نوع الحزمة |

256 كرة BGA |

484 Ball BGA |

256 كرة BGA |

484 Ball BGA |

|

رمز الحزمة |

F256C |

F484C |

FN256C |

F484C |

|

I/O Count |

193 |

317 |

193 |

317 |

|

في النظام قابل للبرمجة |

نعم |

نعم |

نعم |

نعم |

|

دعم الذاكرة المضمنة |

نعم (SRAM/FIFO/CAM) |

نعم |

نعم |

نعم |

|

JTAG (IEEE 1149.1) |

مدعوم |

مدعوم |

مدعوم |

مدعوم |

|

لحظة |

نعم |

نعم |

نعم |

نعم |

|

طلب |

الطاقة المنخفضة ، والمنطق الكثيف |

I/O عالية ، CPLD العامة |

منطق 3.3V المدمجة |

منطق 3.3V عالية السرعة |

LC5768MC-75F256C خطوات البرمجة

1. قم بإعداد لوحتك وأدواتك

قم بتوصيل LC5768MC-75F256C بجهاز الكمبيوتر الخاص بك باستخدام كبل برمجة متوافق مثل Lattice HW-USBN-2B.تأكد من توجيه خطوط JTAG بشكل صحيح ومقاومات الإنهاء (على سبيل المثال ، 4.7kΩ على TCK) موجودة لضمان اتصال مستقر.

2. إنشاء ملف البرمجة

استخدم برنامج Lattice Diamond أو ISPVM لتجميع التصميم الخاص بك وتصدير ملف برمجة Jedec (.jed).يحتوي هذا الملف على Bitstream الكامل الذي سيتم كتابته في ذاكرة تكوين CPLD.

3. قم بتشغيل برنامج البرمجة

افتح مبرمج Diamond أو أداة نظام ISPVM على جهاز الكمبيوتر الخاص بك وتحقق من اكتشاف المبرمج الخاص بك بشكل صحيح.حدد جهاز LC5768MC-75F256C من القائمة لبدء الإعداد.

4. تنفيذ البرمجة داخل النظام (ISP)

استخدم واجهة JTAG (IEEE 1532) لتحميل ملف JEDEC مباشرة في الجهاز بينما يظل مثبتًا على اللوحة.يتم تخزين Bitstream في ذاكرة غير متطايرة داخلية ، مما يتيح التكوين الفوري عند بدء التشغيل.

5. تحقق من التكوين وتأمينه

بعد البرمجة ، قم بإجراء عملية قراءة لتأكيد النجاح.إذا لزم الأمر ، قم بتفعيل فتيل الأمان لقفل الجهاز ومنع إعادة البرمجة غير المصرح به أو الهندسة العكسية.

6. تكوين وإعادة ضبط الجهاز

بمجرد اكتمال البرمجة ، يمكن للجهاز إعادة التشغيل تلقائيًا ، أو يمكنك تبديل برنامجه أو دبابيس init لإجبار إعادة التحميل.ستعمل CPLD بعد ذلك بناءً على التكوين المطبقة حديثًا مع توقيت بدء التشغيل الحتمي.

7. اختياري: إعادة برمجة الحقل أو التحديثات

يمكنك إعادة برمجة LC5768MC-75F256C في الحقل باستخدام واجهة JTAG نفسها للتحديثات أو التصحيحات.بالإضافة إلى ذلك ، تتيح واجهة SysConfig ™ إعادة تكوين جزئي دون ركوب الدراجات في التطبيقات المتقدمة.

LC5768MC-75F256C مزايا

• تشغيل الطاقة المنخفضة للأنظمة المحمولة والمدمجة

بالمقارنة مع العديد من CPLDs التقليدية ذات الفولتية الأساسية العالية ، يساعد LC5768MC-75F256C Low-Power-Power Core في تقليل استهلاك طاقة النظام بشكل عام.هذا يجعلها جذابة للتطبيقات التي تديرها البطارية أو حساسة للحرارة حيث تكون الميزانية الحرارية وكفاءة الطاقة مهمة.

• القدرة الفورية على

على عكس العديد من FPGAs أو الأجهزة الكبيرة القابلة للبرمجة التي تتطلب تكوينًا خارجيًا في كل بدء تشغيل ، يوفر CPLD سلوكًا فوريًا ، مما يسمح بتجنب التأخير أو الحاجة إلى ذاكرة فلاش خارجية.هذا يؤدي إلى أسرع وقت للعملية وموثوقية أكبر.

• توقيت أكثر قابلية للتنبؤ به مقابل FPGAs

يعطي سلوك التوقيت الحتمي لهذا CPLD ، وخاصة تحت أحمال المنطق الثقيل أو I/O ، تحكمًا أفضل مقارنة بالتوقيت المتغير في كثير من الأحيان لـ FPGAs الأكبر.هذا يجعلها أكثر ملاءمة للتطبيقات الزمنية الحرجة مثل حلقات التحكم الرقمية ، وواجهات الاتصال ، وأنظمة المنطق المتزامنة.

• منحنى التعلم الفعال وأداة التصميم النظام البيئي

للانتقال من 22V10s ، أو أقدم PAL/GALS ، أو PLDs البسيطة ، يقدم هذا الجهاز منحنى تعليمي لطيف عبر أدوات تصميم Lattice البديهية مثل Diamond و ISPVM.يستفيد الكثير من النماذج الأولية وأقل من الصداع التكامل.

LC5768MC-75F256C أبعاد التغليف

• نوع الحزمة: صفيف شبكة الكرة الرفيعة

• عدد الدبوس: 256 كرة

• حجم الحزمة: 17mm × 17mm

• ارتفاع الحزمة: حوالي 1.2 ملم

• كرة الكرة: عادة ما يكون الثروة الدقيقة القياسية 0.8 ملم

LC5768MC-75F256C الشركة المصنعة

يتم تصنيع LC5768MC-75F256C بواسطة شعرية Semiconductor Corporation، وهي شركة مقرها الولايات المتحدة معترف بها لخبرتها في أجهزة المنطق القابلة للبرمجة ذات الطاقة المنخفضة.تأسست Lattice في عام 1983 ومقرها في هيلزبورو ، أوريغون ، وتركز على تقديم FPGAs ، و CPLDS ، وأدوات التطوير ذات الصلة المخصصة للتطبيقات في الاتصالات والحوسبة والصناعية والسيارات والمستهلكين.تشتهر الشركة بدورات حياة المنتج الطويلة ، ودعم أدوات التصميم الواسع ، وقابلية الموثوقة في النظام عبر أسر أجهزتها.نظرًا لأن المطور والمورد الأصلي لعائلة ISPXPLD® 5000MC ، تضمن Lattice توثيقًا فنيًا قويًا ودعمًا للبرامج وتوافره من خلال الموزعين المعتمدين وشركاء دورة الحياة على المدى الطويل.

خاتمة

LC5768MC-75F256C هو CPLD ذكي وموثوق يوفر وظائف منطق وذاكرة قوية في شريحة واحدة مضغوطة.يستخدم القليل من القوة ، ويبدأ على الفور ، ويعمل مع العديد من أنواع الإشارات المختلفة.من خلال 768 Macrocells ، والذاكرة المدمجة ، وخيارات الإدخال/الإخراج السريعة ، ومرنة ، فإنها تتناسب بشكل جيد مع منتجات مثل أجهزة الاتصالات والآلات الصناعية وأنظمة التخزين والإلكترونيات الاستهلاكية.تجعل البرمجة السهلة والأداء القوي ودعم التحديثات حلًا مفيدًا لكل من التصميمات والترقيات الجديدة.

معلومات عنا

ALLELCO LIMITED

قراءة المزيد

تحقيق سريع

الرجاء إرسال استفسار ، وسوف نرد على الفور.

أسئلة مكررة [FAQ]

1. هل يمكنني استخدام LC5768MC-75F256C في الأجهزة التي تعمل بالطاقة أو حساسة للطاقة؟

نعم ، يجعل الجهد الأساسي 1.8 فولت وتصميم الطاقة المنخفضة لبيئات LC5768MC-75F256C مناسبة للغاية للبيئات المحمولة ، التي تعمل بالبطارية ، والمقيدة حرارياً ، مثل العقد IoT أو الأجهزة الطبية.

2. هل LC5768MC-75F256C متوافق مع الأنظمة Legacy 5V؟

نعم.حتى مع جهده الأساسي المنخفض ، يتميز LC5768MC-75F256C ببنوك I/O تتحمل 5 فولت ، مما يضمن التوافق مع الواجهات القديمة وأنظمة الجهد المختلط دون الحاجة إلى مكونات لتحويل المستوى الإضافي.

3. ما نوع أدوات التطوير التي يتم دعمها لبرمجة LC5768MC-75F256C؟

يتم دعم LC5768MC-75F256C بواسطة Lattice Diamond ، و ISPVM System ، ومبرمج Diamond.توفر هذه الأدوات دعمًا كاملاً للتصميم والمحاكاة والبرمجة وتصحيح الأخطاء المناسبة لكل من المستخدمين للمبتدئين والمتقدمين.

4. هل يتطلب LC5768MC-75F256C ذاكرة خارجية للعمل؟

لا يلزم وجود ذاكرة خارجية للتكوين.يحتوي LC5768MC-75F256C على ذاكرة غير متطايرة ويدعم القدرة الفورية ، مما يسمح لها بالبدء في التشغيل فورًا بعد الحاجة إلى فلاش خارجي أو EEPROM.

5. هل LC5768MC-75F256C مناسب للبيئات الصناعية القاسية؟

نعم ، مع الأداء المنطقي القوي ، وتحمل الجهد الواسع ، وسلوك بدء التشغيل الموثوق به ، يؤدي LC5768MC-75F256C جيدًا في أنظمة التحكم الصناعية وأتمتة المصنع حيث تكون هناك حاجة إلى تشغيل مستقر.

EPF8820ARC208-4 FPGA دليل: الميزات والهندسة المعمارية والتطبيقات والبرمجة

على 11/07/2025

EPF6016ATC144-2N FPGA: الميزات والبرمجة والتطبيقات والبدائل

على 10/07/2025

الوظائف الشعبية

-

أجهزة الكمبيوتر المعقدة لتعليمات التعليمات: كيف غيرت الحوسبة؟

على 19/04/8000 147783

-

usb-c pinout والميزات

على 19/04/2000 112073

-

باستخدام بدائل المحاكاة الموحدة Xilinx: دليل شامل لتصميم ومحاكاة FPGA

على 19/04/1600 111352

-

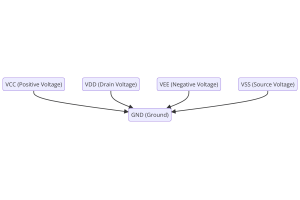

جهد مصدر الطاقة في الإلكترونيات: معنى VCC، VDD، VEE، VSS، وGND

على 19/04/0400 83831

-

دليل موصل RJ45: pinout ، الأسلاك ، أنواع الكابلات ، والاستخدامات

على 01/01/1970 79645

-

الدليل النهائي لرموز الألوان السلكية في الأنظمة الكهربائية الحديثة

الطريقة التي تستخدمها أنظمةنا الكهربائية بالألوان ليست فقط للمظهر.يشير كل لون سلك الآن إلى وظيفة محددة ، مما يسهل تحديد المكونات الكهربائية والتعامل معها بشكل صحيح أثناء التثبيت والصيانة.هذا لا يسر...على 01/01/1970 67013

-

دليل Purge Valve: الوظيفة والأعراض والاختبار والاستبدال لأداء المحرك الأمثل

يعد Purge Valve جزءًا رئيسيًا من نظام السيارة الذي يساعد في الحفاظ على نظافة الهواء من خلال إدارة أبخرة الوقود قبل أن يتمكنوا من الهروب إلى الجو.هذا لا يساعد البيئة فقط عن طريق تقليل التلوث ولكن أي...على 01/01/1970 63136

-

الجودة (س) العامل: المعادلات والتطبيقات

يعد عامل الجودة ، أو "Q" مهمًا عند التحقق من مدى عمل المحاثات والراتين في الأنظمة الإلكترونية التي تستخدم ترددات الراديو (RF).يقيس "Q" مدى تقليل الدائرة إلى تقليل فقدان الطاقة وتؤثر على نطاق التردد...على 01/01/1970 63067

-

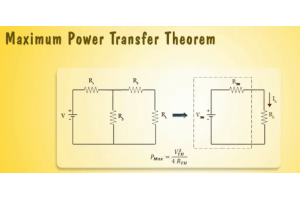

تحقيق ذروة أداء مع أقصى نظرية نقل الطاقة

تشرح نظرية نقل الطاقة القصوى كيف تتدفق الطاقة من مصدر ، مثل البطارية أو المولد ، إلى الحمل المتصل.يوضح الحالة الدقيقة التي يتلقى فيها الحمل أكثر الطاقة.تغطي هذه المقالة ما تعنيه النظرية ، وكيف تعمل...على 01/01/1970 54099

-

مواصفات البطارية A23 وتوافقها

بطارية A23 عبارة عن بطارية صغيرة على شكل أسطوانة مع جهد عالي.يُطلق عليه أيضًا 23a أو 23ae أو Mn21 ، ويتم تشغيله بسرعة 12 فولت وأعلى بكثير من بطاريات AA أو AAA.تصميمه الخاص يجعلها مثالية لل...على 01/01/1970 52228